标签:

看了一段时间的DDR手册,感觉大体有一点了解了,想要实际上板调试,然而实验室可用的开发板不多,拿了一块zynq板看了看,DDR确实有,但是已经集成了控制器,而且控制器还放到了PS端,PL只能通过AXI接口访问。

无奈另外两块开发板也这样,索性就用AXI去控制吧,正好还能再复习一遍AXI。

先简单介绍一下zynq,其全称是ZedBoard Zynq Evaluation and Development Kit , FPGA芯片型号为xc7z020clg484-1。

片内包含一个丰富特性的基于双核ARM Cortex-A9的处理子系统(Processing System,PS)和Xilinx 28nm可编程逻辑(Programmable Logic,PL)。PS除了核心外还包括片上存储器、外部存储器接口以及大量外设连接接口。【引用:Zynq-7000 Overview】

可以看到其存储器规格为:512MB DDR3;256Mb Quad-SPI Flash;4GB SD Card;

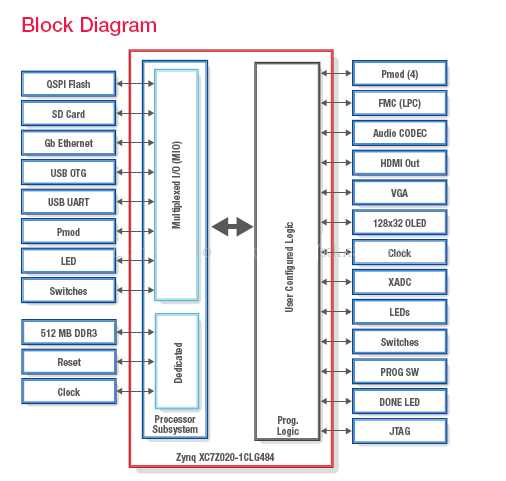

板卡结构框图如下所示:从图中我们也可以明显的看到DDR位于PS端

位于PS端的ARM直接有硬件支持AXI接口,而PL则需要使用逻辑实现相应的AXI协议。Xilinx提供现成IP如AXI-DMA,AXI-GPIO,AXI-Datamover都实现了相应的接口,使用时直接从XPS的IP列表中添加即可实现相应的功能。

有时,用户需要开发自己定义的IP同PS进行通信,这时可以利用VIVADO向导生成对应的IP。VIVADO中用户自定义IP核可以拥有AXI-Lite,AXI-FULL,AXI-Stream。

AXI-Lite具有轻量级,结构简单的特点,适合小批量数据、简单控制场合。不支持批量传输,读写时一次只能读写一个字(32bit)。

AXI4接口和AXI-Lite差不多,只是增加了一项功能就是批量传输,可以连续对一片地址进行一次性读写。

上面两种均采用内存映射控制方式,即ARM将用户自定义IP编入某一地址进行访问,读写时就像在读写自己的片内RAM,编程也很方便,开发难度较低。代价就是资源占用过多,需要额外的读地址线、写地址线、读数据线、写数据线、写应答线这些信号线。

另外一种AXI接口就是AXI-Stream,这是一种连续流接口,不需要地址线(很像FIFO,一直读或一直写就行)。对于这类IP,ARM不能通过上面的内存映射方式控制(FIFO根本没有地址的概念),必须有一个转换装置,例如AXI-DMA模块来实现内存映射到流式接口的转换。AXI-Stream适用的场合有很多:视频流处理;通信协议转换;数字信号处理;无线通信等。其本质都是针对数值流构建的数据通路,从信源(例如ARM内存、DMA、无线接收前端等)到信宿(例如HDMI显示器、音频输出等)构建起连续的数据流。这种接口适合做实时信号处理。

有了上面的这些官方IP和向导生成的自定义IP,用户其实不需要对AXI时序了解太多(除非确实遇到问题),因为Xilinx已经将和AXI时序有关的细节都封装起来,用户只需要关注自己的逻辑实现即可。

标签:

原文地址:http://www.cnblogs.com/christsong/p/5672807.html