标签:

Data Synchronization with Two Same-frequency/Different Phase Clock domains

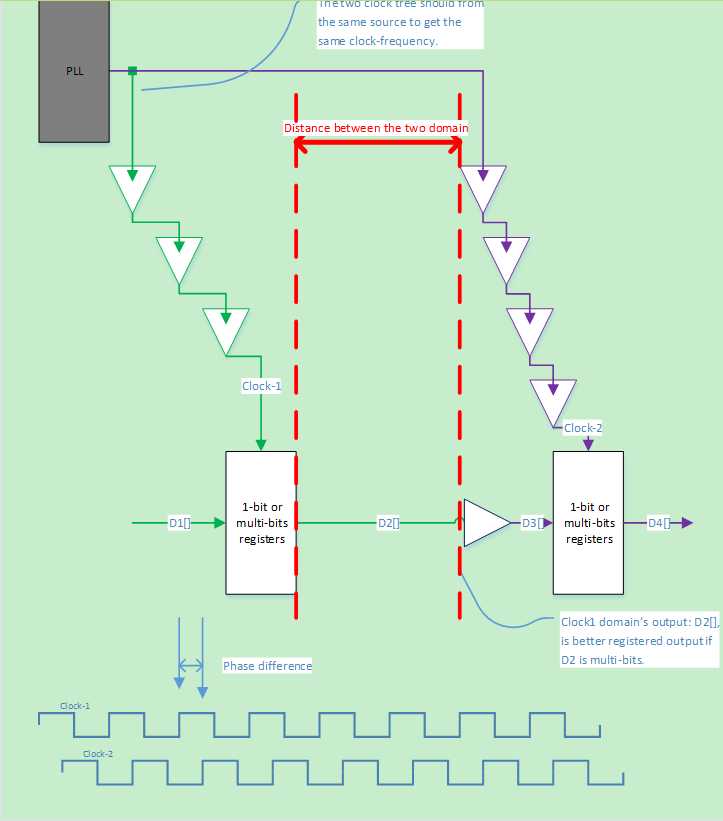

When data is transferred from one clock domain to another clock domain, and the two clock domains are at the same clock-frequency, and are different clock phase for the two clock domain has different clock tree as show below.

From the figure, there are several important points to be highlighted.

This method is benefit area comparing to a-sync-FIFO (the depth should be larger than 8) strategy for both 1-bit and multi-bits width data-synchronization. But the synthesis constraint should be put to the top-level of the 2 clock domains; and timing analysis should be very focus on this.

标签:

原文地址:http://www.cnblogs.com/zhuzhengchao/p/5126209.html