标签:

1 前言

1) What I hear, I forget; What I see,I remember; What I do, I underStand.

2) 理解硬件、软件、编译器、操作系统之间如何交互,透彻理解计算机的内部工作原理。

3) 本书需要的工具和资源下载地址:http://www.nand2tetris.org/software.php

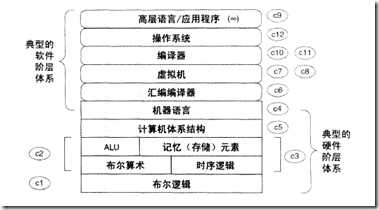

4) 本书涵盖内容

2 基本逻辑门实现

1) Not

/**

* Not gate:

* out = not in

*/

CHIP Not {

IN in;

OUT out;

PARTS:

Nand(a=in,b=in,out=out);

}

2) And

/**

* And gate:

* out = 1 if (a == 1 and b == 1)

* 0 otherwise

*/

CHIP And {

IN a, b;

OUT out;

PARTS:

Nand(a=a,b=b,out=tp1);

Nand(a=tp1,b=tp1,out=out);

}

3) Or

/**

* Or gate:

* out = 1 if (a == 1 or b == 1)

* 0 otherwise

*/

CHIP Or {

IN a, b;

OUT out;

PARTS:

Nand(a=a,b=a,out=tp1);

Nand(a=b,b=b,out=tp2);

Nand(a=tp1,b=tp2,out=out);

}

4) Xor

/**

* Exclusive-or gate:

* out = not (a == b)

*/

CHIP Xor {

IN a, b;

OUT out;

PARTS:

Not(in=a,out=na);

Not(in=b,out=nb);

And(a=a,b=nb,out=tp1);

And(a=na,b=b,out=tp2);

Or(a=tp1,b=tp2,out=out);

}

5) Mux

/**

* Multiplexor:

* out = a if sel == 0

* b otherwise

*/

CHIP Mux {

IN a, b, sel;

OUT out;

PARTS:

Not(in=sel,out=nsel);

And(a=a,b=nsel,out=tp1);

And(a=b,b=sel,out=tp2);

Or(a=tp1,b=tp2,out=out);

}

6) Dmux

/**

* Demultiplexor:

* {a, b} = {in, 0} if sel == 0

* {0, in} if sel == 1

*/

CHIP DMux {

IN in, sel;

OUT a, b;

PARTS:

Not(in=sel,out=nsel);

And(a=in,b=nsel,out=a);

And(a=in,b=sel,out=b);

}

3 多位基本门

1) Not16

/**

* 16-bit Not:

* for i=0..15: out[i] = not in[i]

*/

CHIP Not16 {

IN in[16];

OUT out[16];

PARTS:

Not(in=in[0],out=out[0]);

Not(in=in[1],out=out[1]);

Not(in=in[2],out=out[2]);

Not(in=in[3],out=out[3]);

Not(in=in[4],out=out[4]);

Not(in=in[5],out=out[5]);

Not(in=in[6],out=out[6]);

Not(in=in[7],out=out[7]);

Not(in=in[8],out=out[8]);

Not(in=in[9],out=out[9]);

Not(in=in[10],out=out[10]);

Not(in=in[11],out=out[11]);

Not(in=in[12],out=out[12]);

Not(in=in[13],out=out[13]);

Not(in=in[14],out=out[14]);

Not(in=in[15],out=out[15]);

}

2) And16

/**

* 16-bit bitwise And:

* for i = 0..15: out[i] = (a[i] and b[i])

*/

CHIP And16 {

IN a[16], b[16];

OUT out[16];

PARTS:

And(a=a[0],b=b[0],out=out[0]);

And(a=a[1],b=b[1],out=out[1]);

And(a=a[2],b=b[2],out=out[2]);

And(a=a[3],b=b[3],out=out[3]);

And(a=a[4],b=b[4],out=out[4]);

And(a=a[5],b=b[5],out=out[5]);

And(a=a[6],b=b[6],out=out[6]);

And(a=a[7],b=b[7],out=out[7]);

And(a=a[8],b=b[8],out=out[8]);

And(a=a[9],b=b[9],out=out[9]);

And(a=a[10],b=b[10],out=out[10]);

And(a=a[11],b=b[11],out=out[11]);

And(a=a[12],b=b[12],out=out[12]);

And(a=a[13],b=b[13],out=out[13]);

And(a=a[14],b=b[14],out=out[14]);

And(a=a[15],b=b[15],out=out[15]);

}

3) Or16

/**

* 16-bit bitwise Or:

* for i = 0..15 out[i] = (a[i] or b[i])

*/

CHIP Or16 {

IN a[16], b[16];

OUT out[16];

PARTS:

Or(a=a[0],b=b[0],out=out[0]);

Or(a=a[1],b=b[1],out=out[1]);

Or(a=a[2],b=b[2],out=out[2]);

Or(a=a[3],b=b[3],out=out[3]);

Or(a=a[4],b=b[4],out=out[4]);

Or(a=a[5],b=b[5],out=out[5]);

Or(a=a[6],b=b[6],out=out[6]);

Or(a=a[7],b=b[7],out=out[7]);

Or(a=a[8],b=b[8],out=out[8]);

Or(a=a[9],b=b[9],out=out[9]);

Or(a=a[10],b=b[10],out=out[10]);

Or(a=a[11],b=b[11],out=out[11]);

Or(a=a[12],b=b[12],out=out[12]);

Or(a=a[13],b=b[13],out=out[13]);

Or(a=a[14],b=b[14],out=out[14]);

Or(a=a[15],b=b[15],out=out[15]);

}

4) Mux16

/**

* 16-bit multiplexor:

* for i = 0..15 out[i] = a[i] if sel == 0

* b[i] if sel == 1

*/

CHIP Mux16 {

IN a[16], b[16], sel;

OUT out[16];

PARTS:

Mux(a=a[0],b=b[0],sel=sel,out=out[0]);

Mux(a=a[1],b=b[1],sel=sel,out=out[1]);

Mux(a=a[2],b=b[2],sel=sel,out=out[2]);

Mux(a=a[3],b=b[3],sel=sel,out=out[3]);

Mux(a=a[4],b=b[4],sel=sel,out=out[4]);

Mux(a=a[5],b=b[5],sel=sel,out=out[5]);

Mux(a=a[6],b=b[6],sel=sel,out=out[6]);

Mux(a=a[7],b=b[7],sel=sel,out=out[7]);

Mux(a=a[8],b=b[8],sel=sel,out=out[8]);

Mux(a=a[9],b=b[9],sel=sel,out=out[9]);

Mux(a=a[10],b=b[10],sel=sel,out=out[10]);

Mux(a=a[11],b=b[11],sel=sel,out=out[11]);

Mux(a=a[12],b=b[12],sel=sel,out=out[12]);

Mux(a=a[13],b=b[13],sel=sel,out=out[13]);

Mux(a=a[14],b=b[14],sel=sel,out=out[14]);

Mux(a=a[15],b=b[15],sel=sel,out=out[15]);

}

4 多通道逻辑门

1) Or8Way

/**

* 8-way Or:

* out = (in[0] or in[1] or ... or in[7])

*/

CHIP Or8Way {

IN in[8];

OUT out;

PARTS:

Or(a=in[0],b=in[1],out=tp1);

Or(a=in[2],b=in[3],out=tp2);

Or(a=in[4],b=in[5],out=tp3);

Or(a=in[6],b=in[7],out=tp4);

Or(a=tp1,b=tp2,out=tp5);

Or(a=tp3,b=tp4,out=tp6);

Or(a=tp5,b=tp6,out=out);

}

2) Mux4Way16

/**

* 4-way 16-bit multiplexor:

* out = a if sel == 00

* b if sel == 01

* c if sel == 10

* d if sel == 11

*/

CHIP Mux4Way16 {

IN a[16], b[16], c[16], d[16], sel[2];

OUT out[16];

PARTS:

Mux16(a=a,b=b,sel=sel[0],out=tp1);

Mux16(a=c,b=d,sel=sel[0],out=tp2);

Mux16(a=tp1,b=tp2,sel=sel[1],out=out);

}

3) Mux8Way16

/**

* 8-way 16-bit multiplexor:

* out = a if sel == 000

* b if sel == 001

* etc.

* h if sel == 111

*/

CHIP Mux8Way16 {

IN a[16], b[16], c[16], d[16],

e[16], f[16], g[16], h[16],

sel[3];

OUT out[16];

PARTS:

Mux4Way16(a=a,b=b,c=c,d=d,sel=sel[0..1],out=tp1);

Mux4Way16(a=e,b=f,c=g,d=h,sel=sel[0..1],out=tp2);

Mux16(a=tp1,b=tp2,sel=sel[2],out=out);

}

4) DMux4Way

/**

* 4-way demultiplexor:

* {a, b, c, d} = {in, 0, 0, 0} if sel == 00

* {0, in, 0, 0} if sel == 01

* {0, 0, in, 0} if sel == 10

* {0, 0, 0, in} if sel == 11

*/

CHIP DMux4Way {

IN in, sel[2];

OUT a, b, c, d;

PARTS:

Not(in=sel[0],out=nsel0);

Not(in=sel[1],out=nsel1);

And(a=in,b=nsel0,out=a1);

And(a=a1,b=nsel1,out=a);

And(a=in,b=sel[0],out=b1);

And(a=b1,b=nsel1,out=b);

And(a=in,b=nsel0,out=c1);

And(a=c1,b=sel[1],out=c);

And(a=in,b=sel[0],out=d1);

And(a=d1,b=sel[1],out=d);

}

5) DMux8Way

/**

* 8-way demultiplexor:

* {a, b, c, d, e, f, g, h} = {in, 0, 0, 0, 0, 0, 0, 0} if sel == 000

* {0, in, 0, 0, 0, 0, 0, 0} if sel == 001

* etc.

* {0, 0, 0, 0, 0, 0, 0, in} if sel == 111

*/

CHIP DMux8Way {

IN in, sel[3];

OUT a, b, c, d, e, f, g, h;

PARTS:

DMux4Way(in=in,sel=sel[0..1],a=a1,b=b1,c=c1,d=d1);

DMux4Way(in=in,sel=sel[0..1],a=e1,b=f1,c=g1,d=h1);

Not(in=sel[2],out=nsel2);

And(a=a1,b=nsel2,out=a);

And(a=b1,b=nsel2,out=b);

And(a=c1,b=nsel2,out=c);

And(a=d1,b=nsel2,out=d);

And(a=e1,b=sel[2],out=e);

And(a=f1,b=sel[2],out=f);

And(a=g1,b=sel[2],out=g);

And(a=h1,b=sel[2],out=h);

}

标签:

原文地址:http://www.cnblogs.com/way19/p/5936685.html