标签:大小 方便 一个个 x64 软件 设计 src dir 状态机

在做这个实验的时候在网上找了许多资料,都是关于使用单片机驱动LCD显示,确实用单片机驱动是要简单不少,记得在FPGA学习交流群里问问题的时候,被前辈指教,说给我最好的指教便是别在玩这个了,多看看关于FPGA方面的书籍,比做这个单片机做的东西价值强多了。现在想来确实,自从学习FPGA以来,看过的书没有多少,只是想做个什么了,就在网上找找例程,照抄下来,把算法推理一遍,下个板子实现了,便以为自己会了懂了,要是自己在写一个便问题百出。那么菜鸟始终是菜鸟。自己根本没有掌握FPGA的设计思想和优势,用着FPGA做着单片机的东西,这种东西练练手就足够了,所以,做完这个实验LCD就到此为止了,我也要好好想想该如何进行下面的学习了。在这个上面我还是花费了不少时间,所以写一篇博文总结记录想,回头看的时候,以警醒自己。

做完这个实验我最大的感触是一定要会读数据手册。拿到元件(LCD12864),上面有16个的引脚,先要搞清楚每个引脚的功能,这时候就一定要会读数据手册。我个qc12864b的中文手册琢磨了很久才看懂了一些简单的操作指令,包括在手册上要提取出来,元件的驱动时序,扫描时钟,引脚定义,操作指令,功能描述等。

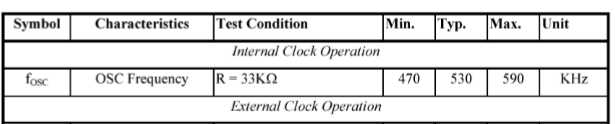

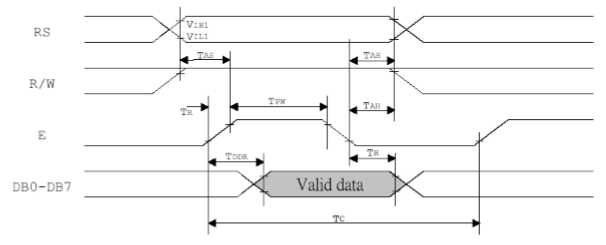

扫描时钟

从手册上可以读出,qc12864b(这是我所使用LCD12864的型号)的扫描时钟介于470—590khz之间,最适为530khz,为了方便分频,所以取500khz。

引脚说明

VSS 电源地,0v -——接开发板GND就行

VDD 电源正极(5v,3.3v)

VO 液晶显示偏压,调整对比度

RS RS=1时,当mpu进行读模块操作,指向地址寄存器

当mpu进行写模块操作,指向指令寄存器

RS=0时,无论进行读/写操作,都指向数据寄存器

R/W 高电平读操作,低电平写操作

E 使能信号,高电平读取信息,下降沿执行命令

DB0 数据总线第0位

DB1 数据总线第1位

DB2 数据总线第2位

DB3 数据总线第3位

DB4 数据总线第4位

DB5 数据总线第5位

DB6 数据总线第6位

DB7 数据总线第7位

PSB 串并控制端口,H为并行,L为串行,直接接5v

RST 液晶复位端口,低电平有效

A 背光正极输入,调整电压大小可以调整亮度

K 背光负极输入,一般直接接地

指令说明

具体指令说明,这里就不一一列出,可查阅qc12864b中文数据手册,我在阅读这一部分的时候耗费了很长时间,这些指令是驱动LCD显示文字与图片的核心,所以必须要掌握。

从时序图可以看出在使能信号的一个周期内可以完成写入数据操作,扫描时钟与使能信号周期相同即可。

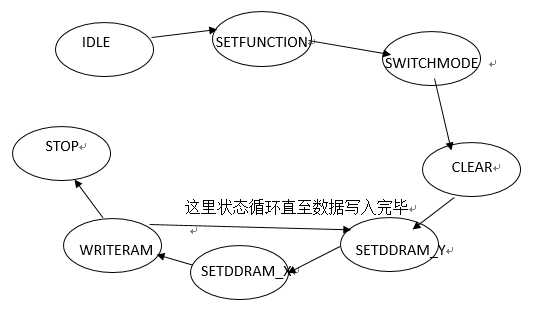

状态转移图

状态机初始化位置 IDLE lcd_data = 8’hzz

功能设计 SETFUNCTION lcd_data = 8’h36//扩充指令绘图显示

显示设置 SWITCHMODE lcd_data = 8’h0c//显示状态

清屏 CLEAR lcd_data = 8’h01//清零指令

设置Y坐标 SETDDRAM_Y

设置X坐标 SETDDRAM_X

写入数据 WRITERAM

结束 STOP

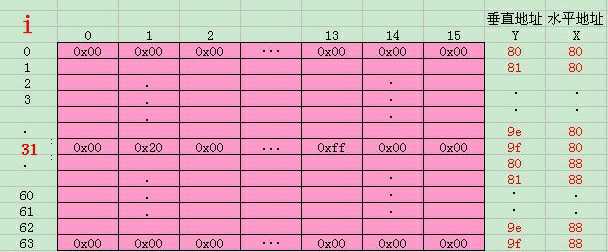

绘图指令下的坐标图

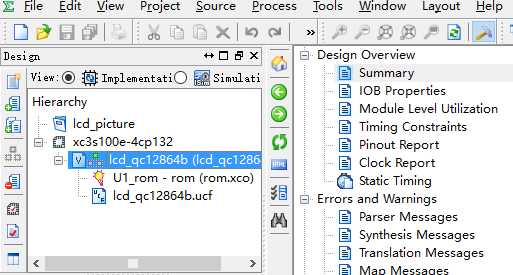

代码如下

lcd_qc12864b

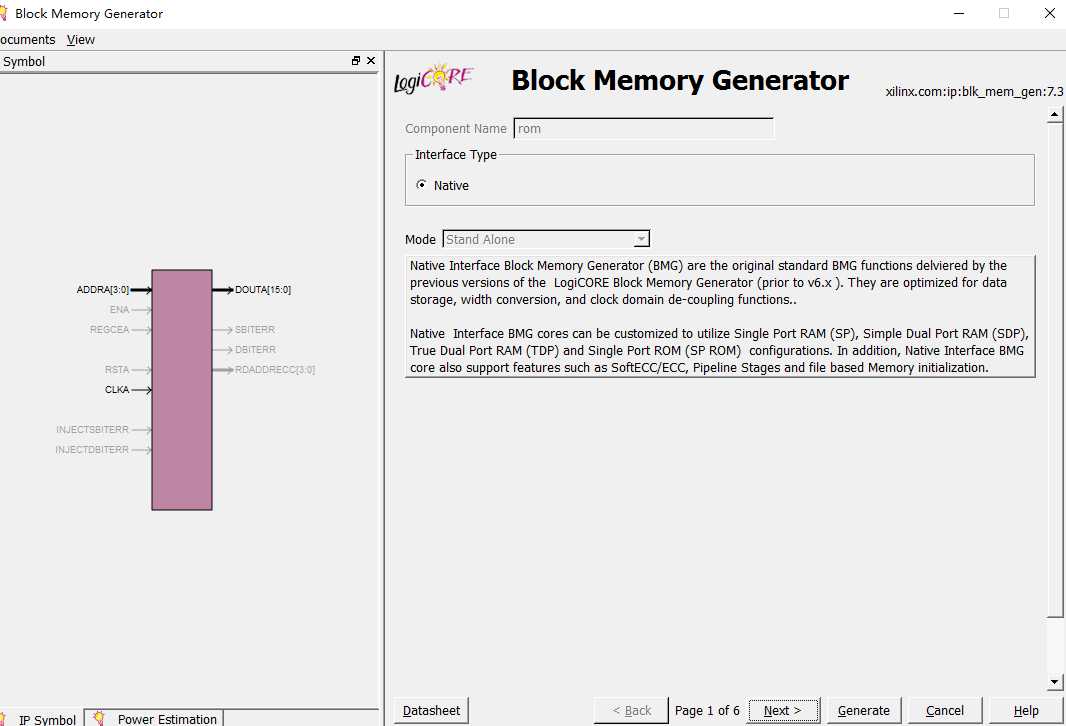

lcd_qc12864b有分布式ROM/ROM和块ROM/RAM,这里配置的是块ROM/RAM。这两种方式具体我也不是了解很深,以后再深入学习。

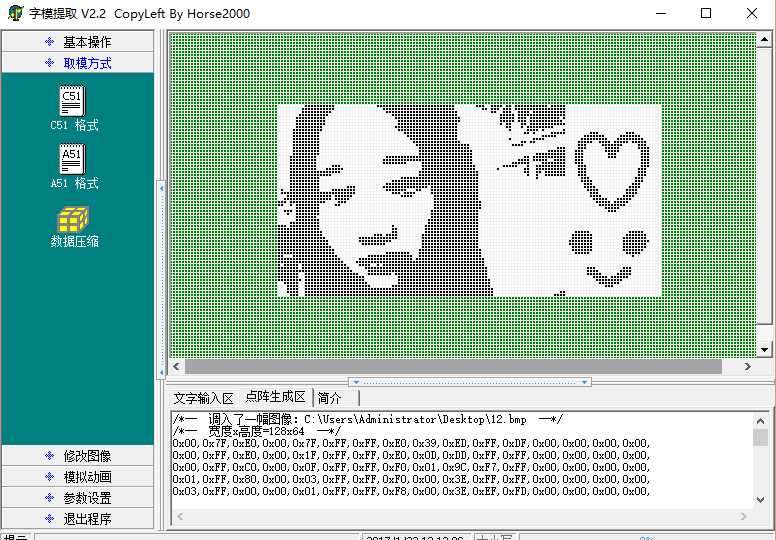

该实验最让我头疼的是调用ROM,第一次接触IP核有许多地方都完全不懂。用LCD(带中文字库)显示文字的时候,可以直接输入文字的十六进制数值,设置显示地址坐标即可,12864显示原理点阵控制点的亮灭来实现,但是如果要显示图片的话一个个输入难免太过麻烦,这个时候调用ROM就方便许多。找一张或做一张像素为128x64的单色图片,使用取模软件,按c51的方式取模。取模出来的数据为十六进制,行8个,64个。

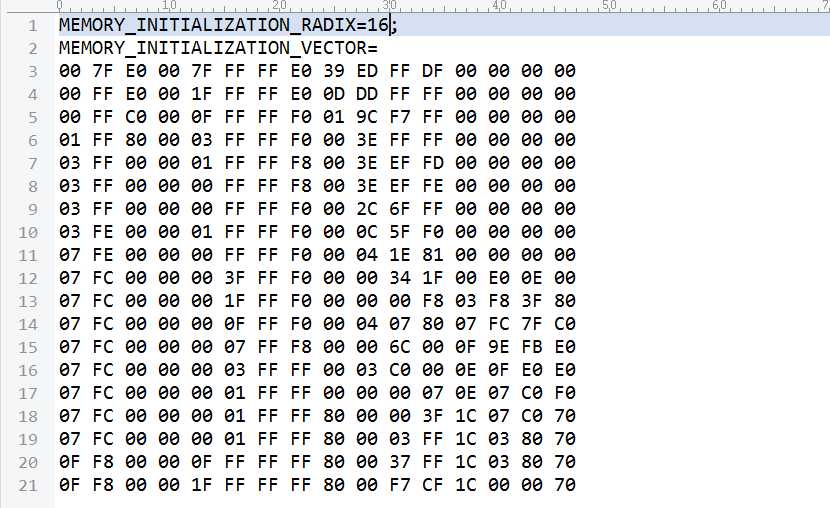

配置块RAM/ROM时,要加载的是.coe文件,所以需要将取模的十六进制数据保存到.coe文件中。最开始我一直在找如何能直接将图片取模出来的数据转化成.coe文件,试了很多方法都失败了,最后发现完全可以自己按文件格式编辑一个即可,最终文件保存格式如下。

将图片取模出来的每个数据前的ox去掉,这只是C语言中16进制的表示形式,文件第一行的MEMORY_INITIALIZATION_RADIX=16;表示数据全都为16进制数,这里的16可以换成8、2、10都行。

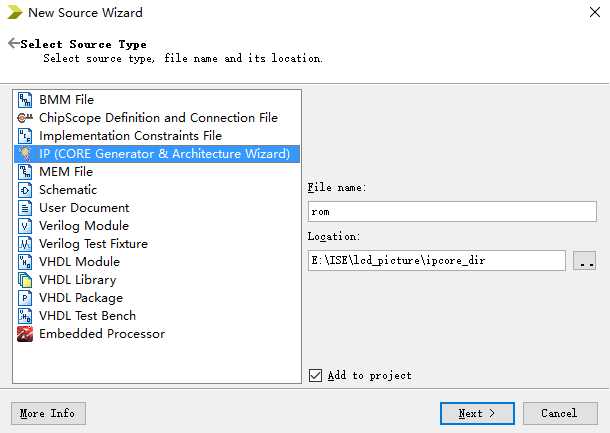

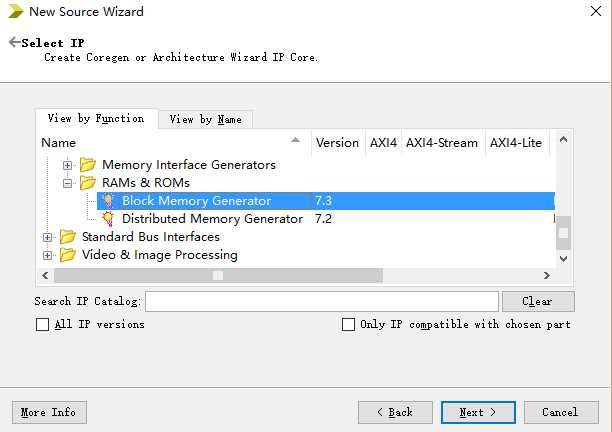

打开ISE建立工程后,新建文件,选择IP(CORE Generator & Architecture Wizard),填写文件名,next

找到Memories & Storage Elements单击,选择RAMs & ROMs单击,选择Block Memory Generator 7.3,next,finish。

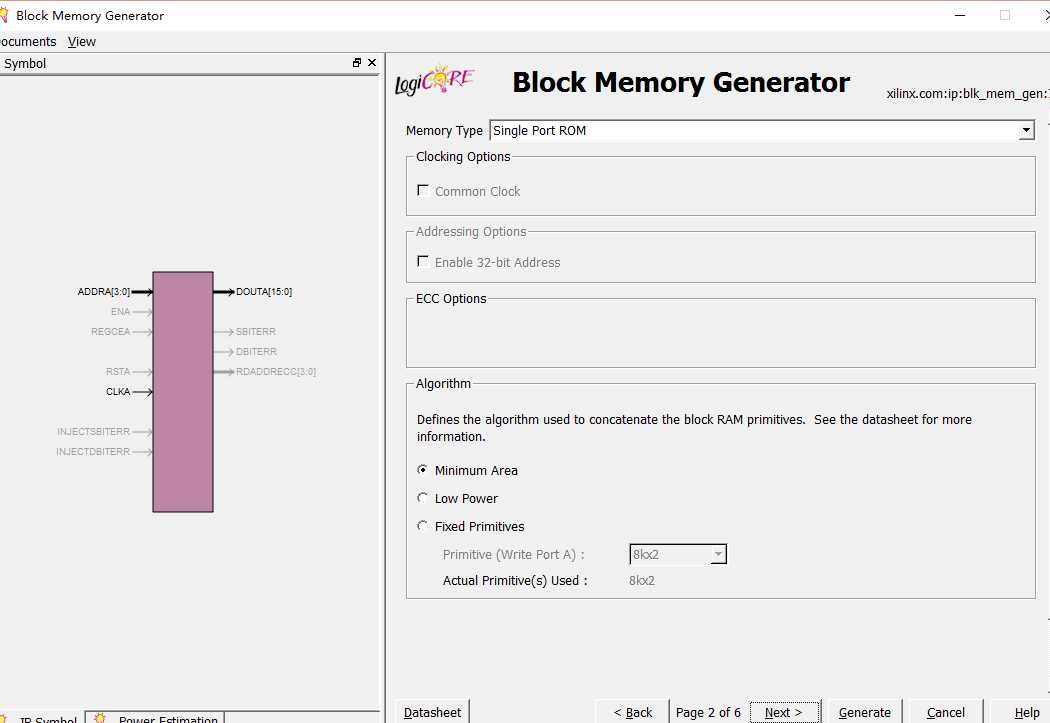

上面直接next,下面这里选Single Port ROM,next

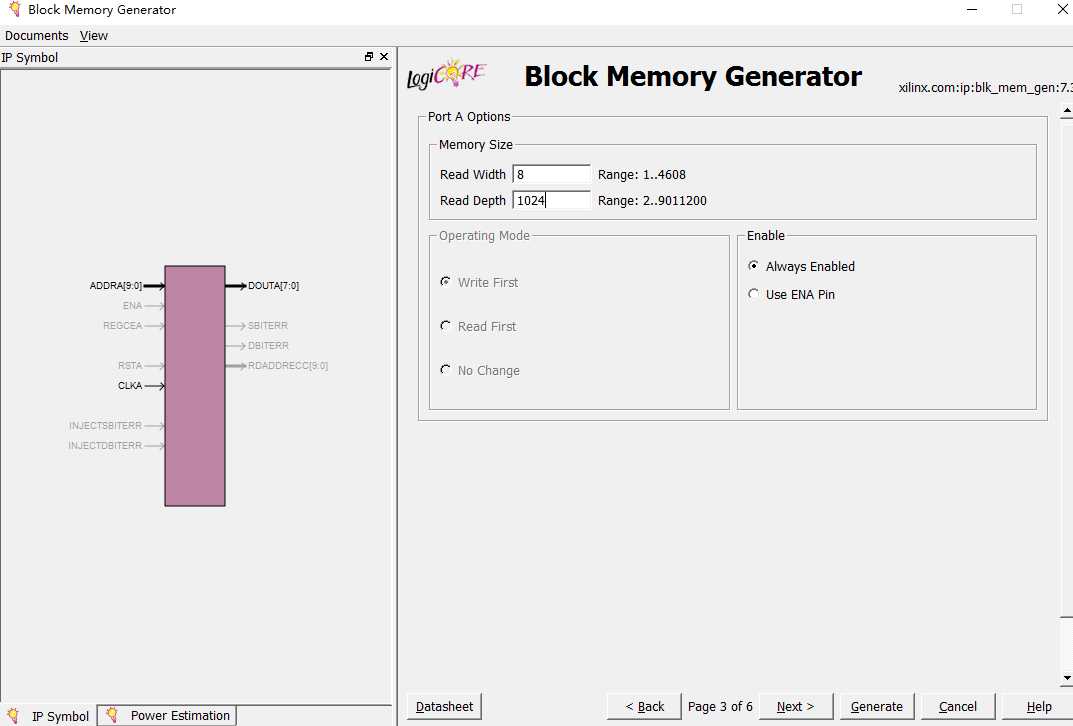

这里要填写数据位宽和深度,位宽是你所需要输出的数据位宽,LCD有8个数据位,故这里定义位宽为8,深度即有多少个这样的数据,从取模出来的数据看,易得共有1024个数据位。我使用的basys2开发板使用的是Xilinx Spantan3E—100TQ144 FPGA包含73728位的块RAM/ROM。因此,使用的块RAM的最大容量为9216字节或4608个16位字。从这里来看,是完全够用的。

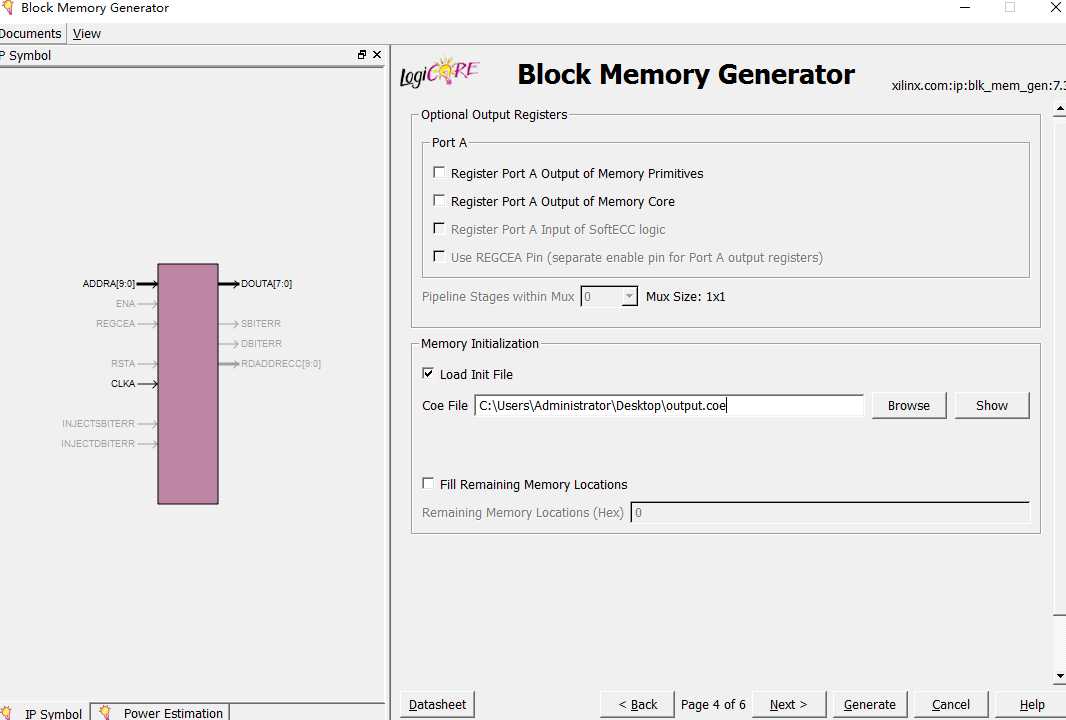

Next,加载.coe数据文件,勾选Load Init File 加载.coe文件,我这里是在桌面上保存着,直接找到选择就好。

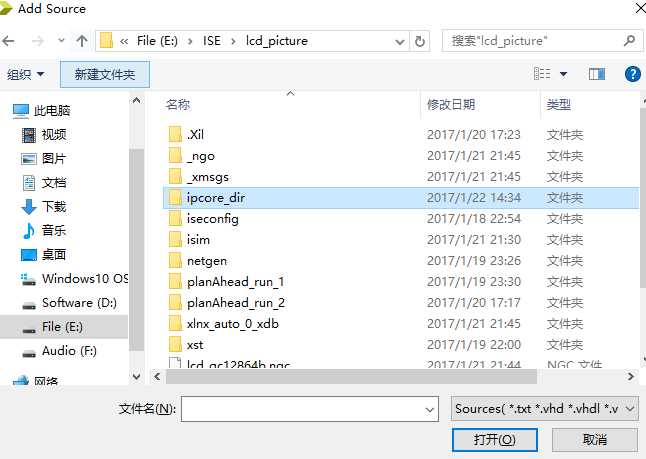

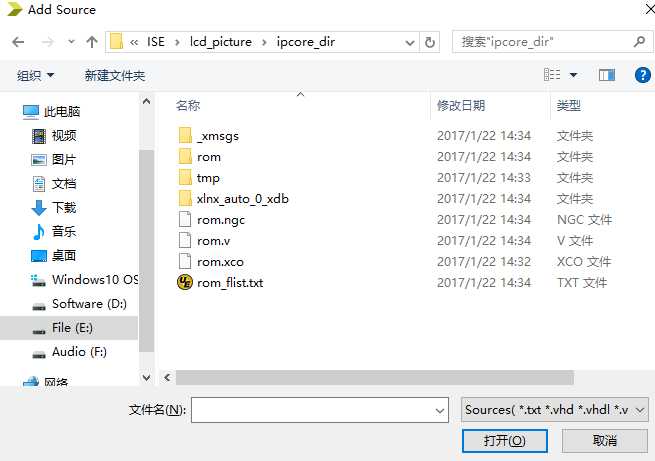

然后一直点击next直至最后一个界面,最后点击Generate,生成rom.xco。生成的IP核在工程目录下的ipcore_dir文件中。

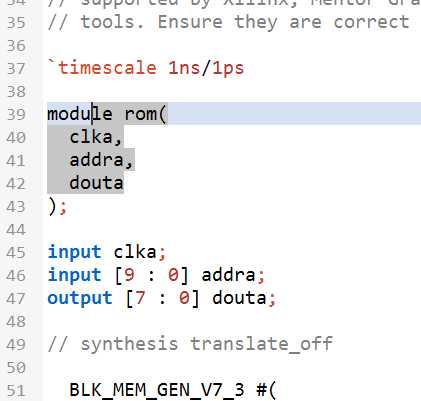

将rom.v文件打开端口定义如下,直接在顶层文件对其实例化,如代码所示

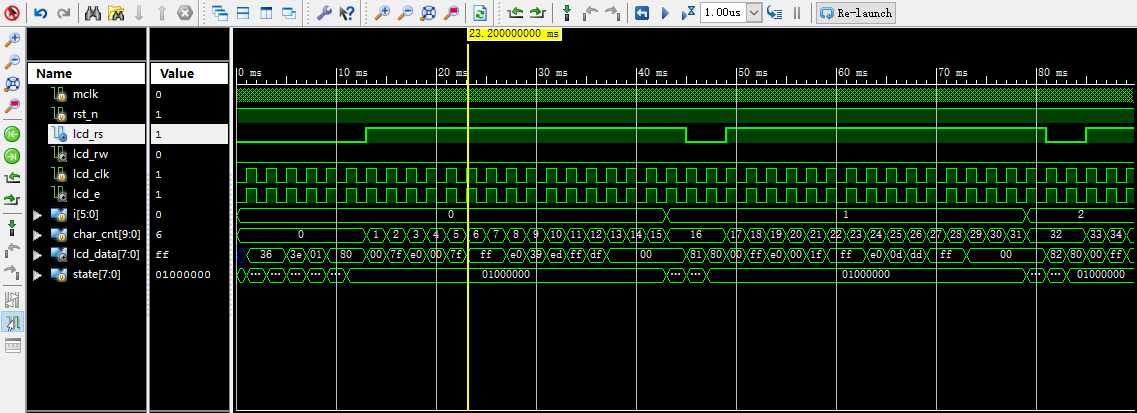

最后可直接仿真,新建tb文件查看仿真传输数据是否正确。由波形图可得在功能设定指令传输完毕后,进入读数据状态,所读入的数据与文件中数据相符,一行数据传输完毕进入下一行,继续读入数据,仿真图结果正确。下板子也正确。

最开始学习FPGA,最容易出现的就是两个问题,一个是把verilog当C语言来写,另一个就是把FPGA当单片机来用。前者我已经有了改善,后者我还需要继续努力。

基于basys2驱动LCDQC12864B的verilog设计图片显示

标签:大小 方便 一个个 x64 软件 设计 src dir 状态机

原文地址:http://www.cnblogs.com/chenliyang/p/6547750.html