标签:长度 splay 需要 应用 计算 链路 耦合 ref toc

文章目录 [显示]

要想了解在使用分辨率等于或高于 12 位 ADC 时可能发生的问题,需要确定 ADC 能够处理多小的电压值。电压范围为 2 V 的 8 位 ADC 能够检测最小电压值为 2 V/256 = 0.008 V,即 8 mV 左右。尽管 8 mV 看上去比较小,让我们把这个值和更高分辨率的 ADC 进行比较,表 1 显示了对具有输入范围为±1 V 和分辨率为 8 到 20 位的各 ADC 进行的比较。

当分辨率为 20 位时,ADC 能够处理最小为 2 μV 的电压。稍微提高增益,您可以处理低于 1 μV 的电压。另外,包含窄输入范围(高 ADC 增益)的低分辨率 ADC 系统也可以处理微伏范围的电压值。

使用低分辨率ADC时,1 mV以下的偏移和噪声源是无意义的。但使用12位到20位ADC时,该值将起着重要作用。 未习惯于敏感模拟电路的设计师会容易忽略这些偏差。目前的电子产品越来越小,因此单是较小的电路板几何形状就能引起许多问题。

当 PCB 缩小时,走线宽度会更窄,距离更加接近。目前的电子产品中走线宽度和走线之间的间隙一般不超过 6 密耳

(0.006 英寸)。即使您指定了大小为 6 密耳的走线,仍可以通过过度蚀刻轻松地使该值降至 4 或 5 密耳。 那么,为什么我们需要留意走线变小的现象?当走线变窄时,走线电阻会增加。公式 1 提供了计算走线电阻的标准公式:

PCB 上走线的厚度为 1 盎司铜,长度为 1 英寸,宽度为 8 密耳,其电阻将为 0.062 欧姆。表 2 显示的是针对若干走线长度和宽度计算得出的阻抗值。

如表 2 中所示,所有的阻抗都大大低于 1 欧姆。这看上去对电路影响并没有那么大,但具体情况取决于该走线在电路 板上的位置。如果是高阻抗放大器输入的走线,就没问题,但在其他情况下,就会产生影响。再次使用该表并为每个走 线组合通过 5 mA 的电流。虽然 5 mA 的电流不大,并且走线电阻不到 1 Ω,但在使用高分辨率的 ADC 时,组合偏移 会变得十分显著,如表 3 所示。

在该表里,如果流入走线(其宽度为 6 密耳,长度为 2 英寸)的电流为 5 mA,则电压将为 820 μV,即 0.82 mV 左 右。在表 1 中,请注意,在系统采用的 ADC 分辨率低于 12 位时,该电压并不显著。绿色显示的单元是至少影响到 16 位 ADC 半个最低有效位的条件。黄色显示的单元表示在使用 12 位或更高 ADC 时导致相同偏差的条件。这时,假设 12 位和 16 位 ADC 的输入范围为 2 伏特(+/- 1 伏特)。

一个示例应用(其中该偏移大小引起显著偏差)是使用热电偶来测量温度。如果使用 K 型热电偶,输出电压将为 40 μV/°C左右。那么,410 μV偏移相当于超过10°C的偏差。如果相同走线被过度蚀刻,使其宽度降至4密耳,偏差 将增加 50%。通过该示例,可以看到评估信号路径中的每个 PCB 走线的重要性。虽然 12 位 ADC 不是最坏情况,但如 果 ADC 前面增加 16 倍的增益,相应的电压分辨率等价于 16 位 ADC。

设计带有混合信号或高精度 ADC 的电路板时, 需要识别电流在 PCB 中的具体位置。走线上几毫 安(mA)的电流就能造成严重的问题。

当数字器件或高电流模拟器件共享敏感模拟信号的 返回路径时,走线电阻就会对电路产生影响。此情 况下,高电流的单位不再是安培(A),而是毫安 (mA)。在前一示例中,热电偶与 5 mA 负载共 享一个返回路径。即使将该负载降至 0.5 mA,偏 差仍然为 1 °C。因此,几百 μA 的电流影响也比较大。

图 1 显示的是一个示例,其中模拟接地和数字接 地共享一个返回电流路径,传感器和 LED 共享另 一个返回电流路径。这两个共享路径可能会导致系 统偏移或增益偏差问题。

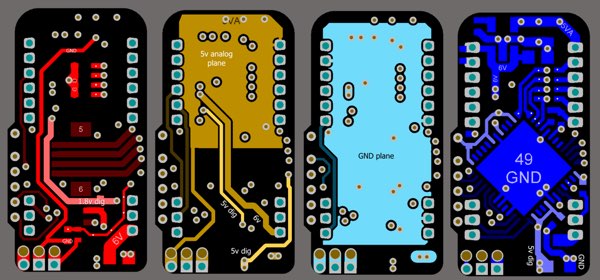

当本示例中的 ADC 测量传感器的输出电压时,它 也会测量走线电阻上的电压。共同接地处与传感器 电流和 LED 电流合并的位置之间的走线长度越 大,可能发生的电压偏移越严重。该偏差的严重性 取决于系统所需的准确度、传感器的电压增益以及 偏移偏差电压的大小。图 2 显示的是 PCB 布局的 一个示例。

模拟地(VSSA)和您正在测量的所有信号一样, 起着重要作用。PSoC 的 VSSA 引脚与系统地处之 间的走线长度及其阻抗必须尽可能小。即使几百 微安(μA)的电流分量共享该路径,当测量几个 毫伏的信号时,也会导致许多问题。使用单端测量 时,这里的偏移可以被视为测量偏移。在图 3 中,LED 的电流与供电电流共享一个路径,但传 感器使用它自己的路径。内部带隙参考电路也被连 接到 VSSA。因与 LED 共享返回路径而消耗的任何 电压都会使 ADC 参考电压产生波动,电压下降的 大小为 I*R。参考电压和 VSSA 之间的偏移会导致 ADC 增益偏差。

为数字接地(VSSD)、模拟接地(VSSA)、传感 器和 LED 提供单独的接地路径后,将没有共享返 回路径(参考图 4)。该传感器、ADC 和参考电 路都被连接到同一个模拟接地,因此 LED 中的电 流变化几乎不会对传感器的输出产生任何影响。另 外还要注意,在该图中,传感器和 VSSA 在同一个 位置上与模拟接地相连。该接地连接的地理位置可 以是一个点,或者是极低的阻抗层。

通过将差分 ADC 连接到传感器,可以消除传感器 返回和高电流共享一个路径时导致的共模电压偏 移;请参看图 1。普通电压是指传感器 Vss 和传感 器输出的普通偏移。然而,该传感器的差分连接不 能降低 VSSA 共享接地路径时产生的偏差 (图 3)。请参看图 5。

图 6 显示的是一个改进路由的示例,包括单独的 返回路径、单独的模拟和数字电源,以及传感器的 差分连接。

当传感器共享返回路径或调制负载(如 PWM 驱动 的 LED)共享 VSSA 引脚时,可能不会立即发现偏 差。如果调试负载与 ADC 完全同步,生成的偏差可 能大,也可能小。如果同步化过程中没有产生任何 可测量的偏差,那么,开始开发和测试时,不会发 现任何问题。但如果在这种情况下修改了 ADC 采样 率或 PWM 频率,偏差或噪声将发生明显的变化。 这样的变化难以测试,因为在许多应用程序中,负 载调制会根据不同的环境或软件而有所变化。因 此,一个电路板设计有时候能够正常运行,有时候 则无法工作。因此,即使设计能够正常工作,仍然 需要遵循良好的设计规则。

理想情况下,模拟和数字信号将位于电路板的对立 侧上,但这种情况一般不会发生。许多设计都要求 模拟和数字信号位于同一个区域内。遗憾的是,在 一个区域内同时运行较高阻抗的模拟信号和数字信 号可能引起意外串扰,该串扰给模拟信号带来过大 噪声。

串扰指的是没有直接相连时,一个信号对另一个信 号产生影响的现象。具有快速上升和下降时间的数 字信号对高阻抗的模拟信号路径产生影响是最常见 的串扰现象。数字信号同样受串扰的影响。高速数 字信号容易影响到其他数字信号。各信号之间的串 扰类型为:传导、容性或者感性。在所有情况下, 通过加大各信号之间的距离并缩短它们之间并行的 长度,可以减少信号串扰。

传导串扰的影响一般不大。只有各信号的阻抗过高 (超过 10 MΩ)时,这种串扰才会造成问题。当 PCB 上出现泥土、油、盐或其他液体异物,增大了 各走线之间的 PCB 材料的导电性时,通常会发生高 传导串扰情况。阻抗下降所导致的串扰会对电路操 作产生不利影响。在某些情况下, 焊接掩模可以保 护 PCB。但始终会有裸露区,如 PCB 上器件焊接 的位置。如果在使用产品的环境中发现这些材料, 必须采用各种措施使 PCB 与这些材料隔离。如果不能使 PCB 与异物隔离,可以在 PCB 上使用外部涂料,但该方法会增加费用。

当一个走线位于其他层中另一个走线的正上方时, 将发生容性耦合。铜线之间形成一个电容。这些铜 线重叠部分越多,它们耦合形成的电容越高。通过 减少各信号之间的重叠区降低该电容,从而减少耦 合。在某些情况下,特别是在双层电路板上,几乎 不能消除敏感模拟信号与快速数字信号交叉的情 况。这时,这些信号需要以 90 o 的角度交叉,以尽 量减少它们之间形成的电容。

如果使用两层以上的多层电路板,请保证两个相交信号之间存在电源层,以尽可能减少耦合。请注 意,图 7 中的电容在两个走线之间形成,它与重叠区成正比。

如果使用多层电路板,请确保模拟和数字走线以 90° 的角度相交。这样可大大减少重叠区,从而降低各 信号之间的容性耦合。图 8 显示的是一个示例。

图 9 显示的是 PCB 布局的一个示例,其中模拟走线 (红色)必须与数字走线(蓝色)交叉。请注意, 模拟和数字走线之间为 90°。

在同一层或相邻层上运行的各条走线可能被磁耦 合。该情况被称为感性耦合。感性耦合由三个机械 特性引起。这些特性为:各走线之间的分离、两个 并行走线之间的距离、走线和其最接近电源层的距 离。各信号之间的距离以及各信号和接地层之间的 距离都是影响最大的因素,如公式 2 和图 10 所示。

正如您能够发现,走线和接地层之间的距离(即为 高度)是一个重要因素。通过缩短该距离,可能以 高度平方的数值降低串扰。如果需要运行相邻的数 字和模拟走线,那么,使它们接近于接地层会是降 低串扰的最好方法。

3 W 规则规定了各逻辑走线(中心到中心)之间的 距离必须为走线宽度的三倍。例如,如果 PCB 上走 线的宽度为 0.008 英寸,则两个相邻走线中心之间 的距离将为 0.024 英寸(0.008 英寸 x 3),其边缘 的距离为 0.016 英寸(0.008 英寸 x 2)。这样可使 每个走线处在另一个走线的 70%磁通量边界范围 外。为了能够位于 98%磁通量边界的范围外,两个 相邻走线之间的距离必须为走线宽度的 10 倍。这些 条件都取决于各走线的阻抗以及各信号的上升时 间。请参看图 11。

减少(在电路板同一侧上运行的相邻)信号之间的 耦合的另一个方法是在这些信号之间放置一个防护 线,并将之接地。这样可以减少各信号之间的容性 耦合。请参看图 12。

在多层电路板中,各层之间的距离不一样。例如, 在厚度为 0.062 英寸的 4 层电路板中,与第二层和 第三层之间的距离相比,第一层和第二层之间的距 离更小。因此,在同一个区域内走模拟和数字信号 时,请将各走线分布到非相邻层上,可以尽可能扩 大它们之间的距离。

在敏感模拟系统中,需要将模拟电源和数字电源分开。一般建议使用独立的外部模拟和数字电压调节器。如果额外电压调节器的成本过高,并且您的设计中数字部分不包括高速或 高电流切换功能,可以使用单个电压调节器。就如您拥有独立的调节器时,要注意要在设计上始终隔离模拟和数字的电源电 路。分别为模拟电源(VDDA、VSSA)和数字电源(VDDD、VSSD)提供独立的电源和接地信号。请尽可能缩短这两个电源 (模拟和数字电源)与电路板电源之间连接的距离。电路板电源的输出阻抗一般较低,所以通过上述连接,数字电源几乎不 会对模拟电源产生影响。

接地层在混合信号设计中始终有用,但对于某个已给的设计,额外层成本较高。即使在双层电路板中,也可以在敏感模

拟部分添加部分层。无论您是否使用接地层,都需要确保返回路径与电源之间的连接最短。请注意,如果接地层电源电

路的阻抗不够低,或者过度分散该层,则不能利用该层改善您的设计。在双层电路板上,不要仅仅依靠最后的地平面填

充,因为这样可能带来高阻抗的接地路径。如不仔细检查,很难发现这样的缺陷。比较好的设计习惯是,先通过走线布

局好接地路径,然后进行地平面填充。

如果在您的设计中能够使用单独的模拟和数字接地层,那么几乎在所有情况下,它们需要在一个单点上相连。该单点需 要位于电源和 SoC 器件之间。

当仅用一个单电压调节器时,只在模拟和数字组件相互隔离的情况下,对地平面可以不做分割。

用于电源稳定性的电容有两种:旁路电容和大容量电容。有些时候大容量电容还被称为储能电容。旁路电容必须位于组 件电源引脚附近。使用旁路电容可以消除高频噪声并为瞬间变换提供电流。这些电容的取值范围为 0.001 μF 到 0.1 μF。 NPO、X5R 及 X7R 等介电电容是优良的旁路电容。这些电容的取值范围为几百皮法(pF)到几微法(μF)。

储能电容通常位于电压调节器附近。如果电路板的较大(超过几平方英寸),并各处都有一些有源器件,那么,这些电 容将分布在整个电路板上。储能电容可以在较长时间内供电,并可以滤除低频噪声。在具有高电流信号或电源的电路板 中,储存电容的取值范围为 1 μF 到 100 μF,或更大的值。X5R、钽和一些表面组装电解电容都适合该用途。

旁路电容一般只为 0.01 μF 或 0.1 μF。推荐进行一些简单的计算操作,以得到最佳的储能电容。如果该值过高,则表示 储能电容超过您所需要的电容。如果该值太低,会使电源纹波过大并造成噪声。请使用下面公式:

当为各种应用选择一个电容(甚至一个简单的旁路电容)时,它的规范是非常重要的。电压和温度系数是两个最常被忽略的电容规范,但能够在正常操作的环境下大大影响器件电容。

器件变得越来越小,需要对性能和大小进行权衡。标称值为 1 uF,耐压为 6.3 V 的电容,在电压为 5 V 时,电容值可 以小于 0.1 uF。因此,您需要注意电压系数。另外,不假设全部器件系列的电压系数是相同的。电压系数和温度系数 可以因不同封装而有大变化。与 0603 封装相比,0805 封装具有较好的电压系数,但有时会反过来。因此请阅读数据 手册。如果数据手册中没有提供电容器的温度和电压系数,请考虑使用其他制造商的电容器。

设计混合信号的电路板时,必须遵循下列规则:

PCB 布局工具有 20 年的使用历史。通过使用这些工具可以对各信号进行分组,并为走线长度和各走线之间的距离提供 不同的规则。从而避免发生错误。自动布线越来越强大,并具备许多个常用工具。这些工具遵循手动路由时所要求的相 同规则。熟练的 PCB 布局设计师可以使用这些规则来提高自动布线的性能。虽然这些工具非常强大,但仍需要特别注 意模拟和数字信号的布线方式。特意推荐您先手动走电路板上的敏感部分,然后才通过自动布线走剩下的其他不重要部 分。不管使用哪个方式,都要确保检查最后布线。

将各器件放置在最佳的位置对手动布线和自动布线都有很大的帮助。器件放置和电路板布局都安排好后,可以使用简单 的测试来验证共享返回路径是否存在问题。打印该电路板布局并在电源和每个组件之间画出最直接的路径。为模拟组件 和数字组件分别使用两种不同的颜色。如果这两种颜色交叉,需要重新评估您的设计。请参考图 19。

标签:长度 splay 需要 应用 计算 链路 耦合 ref toc

原文地址:http://www.cnblogs.com/zheming/p/6675411.html