标签:extern color 为什么 就会 for nbsp 成功 电源 参考

本章参考资料:《 STM32F4xx 中文参考手册》 RCC 章节。

学习本章时,配合《 STM32F4xx 中文参考手册》 RCC 章节一起阅读,效果会更佳,特

别是涉及到寄存器说明的部分。

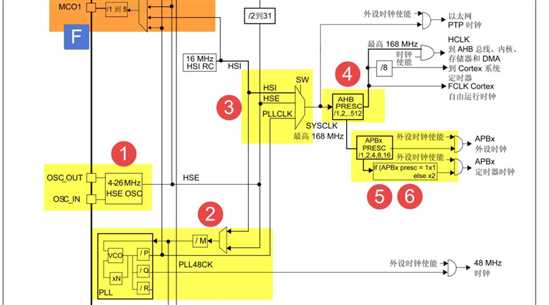

RCC : reset clock control 复位和时钟控制器。本章我们主要讲解时钟部分,特别是要

着重理解时钟树,理解了时钟树, F429 的一切时钟的来龙去脉都会了如指掌。

HSE时钟

HSE:High Speed External Clock signal,即高速的外部时钟。

来源:有源晶振(1-50M)、无源晶振(4-26M)

控制:RCC_CR 时钟控制寄存器的位16:HSEON控制

HSI时钟

HSI:High Speed Internal Clock signal,即高速的内部时钟。

来源:芯片内部,大小为16M,当HSE故障时,系统时钟会自动

切换到HSI,直到HSE启动成功。

控制: RCC_CR 时钟控制寄存器的位0:HSION控制

问题:有源晶振和无源晶振的区别?

为什么要通过PLL到180M而不直接接180M的晶振?

无源晶振有2个引脚,需要借助于外部的时钟电路(接到主IC内部的震荡电路)才能产生振荡信号,自身无法振荡。

有源晶振有4个引脚,是一个完整的振荡器,其中除了石英晶体外,还有晶体管和阻容元件.只需要电源,就可输出比较好的波形。

晶振频率越高,受温度的影响越大,这是制造工艺决定的....所以一般是外部接8-12M的晶振,然后内部锁相环升频,就会得到高频的时钟信号。

锁相环时钟

锁相环时钟:PLLCLK

来源:HSI、 HSE。由PLLSRC位配置。

HSE或者HSI先经过一个分频因子M进行分频,然后再经过一个

倍频因子N,然后再经过一个分频因子P,最后成为锁相环时钟

PLLCLK = (HSE/M) * N / P = 25/25 * 360 / 2 = 180M

控制: RCC_PLLCFGR :RCC PLL 配置寄存器

PLL48CK:USB_FS、 RANG、 SDIO提供时钟

系统时钟

缩写:SYSCLK,最高为180M,F407最高为168M。

来源:HSI、 HSE,PLLCLK。

控制: RCC_CFGR 时钟配置寄存器的SW位

HCLK时钟

HCLK:AHB高速总线时钟,最高为180M。为AHB总线的外设

提供时钟、为Cortex系统定时器提供时钟(SysTick)、为内核

提供时钟(FCLK)。

AHB为advanced high-performance bus。

来源:系统时钟分频得到。

控制: RCC_CFGR 时钟配置寄存器的HPRE位

PCLK1时钟

PCLK1:APB低速总线时钟,最高为45M。 为APB1总线的外设

提供时钟。 2倍频之后则为APB1总线的定时器提供时钟,最大

为90M。

来源:HCLK分频得到。

控制: RCC_CFGR 时钟配置寄存器的PPRE1位

PCLK2时钟

PCLK2:APB高速总线时钟,最高为90M。为APB2总线的外设

提供时钟。 2倍频之后则为APB2总线的定时器提供时钟,最大

为180M。

来源:HCLK分频得到。

控制: RCC_CFGR 时钟配置寄存器的PPRE2位

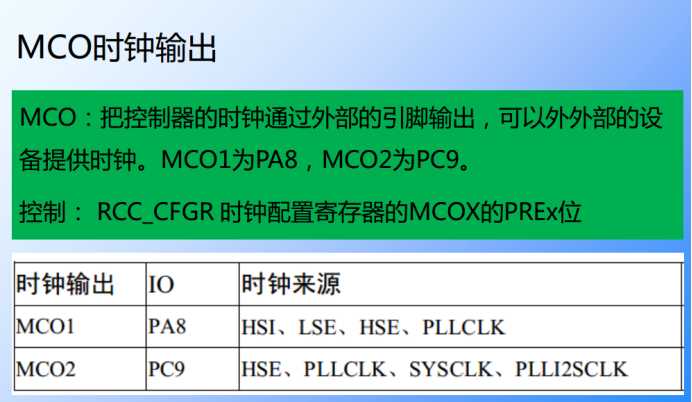

RTC时钟

RTC:为芯片内部的RTC提供时钟。

来源:HSE_RTC(HSE分频得到)、 LSE(外部32.768KHZ的晶

体提供)、 LSI(32KHZ)。

控制: RCC备份域控制寄存器RCC_BDCR:RTCSEL位控制

独立看门狗时钟:IWDGCLK,由LSI提供

I2S时钟:由外部的引脚I2S_CKIN或者PLLI2SCLK提供。

以太网PHY时钟:429没有集成PHY,只能外接PHY芯片,

比如LAN8720,那PHY时钟就由外部的PHY芯片提供,大小

为50M。

USB PHY时钟:429的USB没有集成PHY,要想实现USB高

速传输,只能外接PHY芯片,比如USB33000。那USB PHY时

钟就由外部的PHY芯片提供。

完整时钟树参考手册。

不得不说,ST给我们做好固件库之后,开发速率直线提升,比起2440好上手,这种时钟配置不需要我们关心,但2440什么都要自己来,相辅相成。

F103 系列中,使用 HSI 最大只能把系统设置为 64M,并不能跟使用 HSE 一样把系统

时钟设置为 72M,究其原因是 HSI 在进入 PLL 倍频的时候必须 2 分频,导致 PLL 倍频因子

调到最大也只能到 64M,而 HSE 进入 PLL 倍频的时候则不用 2 分频。

在 F429 中,无论是使用 HSI 还是 HSE 都可以把系统时钟设置为 180M,因为 HSE 或

者 HSI 在进入 PLL 倍频的时候都会被分频为 1M 之后再倍频。

还有一种情况是,有些用户不想用 HSE,想用 HSI,但是又不知道怎么用 HSI 来设置

系统时钟,因为调用库函数都是使用 HSE, 下面我们给出个使用 HSI 配置系统时钟例子,

起个抛砖引玉的作用。 BH有个参考历程,如果需要可以参考修改。

标签:extern color 为什么 就会 for nbsp 成功 电源 参考

原文地址:http://www.cnblogs.com/yangguang-it/p/6791915.html