标签:串口通信 方法 back 数据 时钟 问题 需要 比较 logs

一、 流水线设计

将原本一个时钟周期完成的较大的组合逻辑通过合理的切割后分由多个时钟周期完成。该部分逻辑运行的时钟频率会有明显对的提升,提高系统的性能用面积换速度

一个流水线设计需要4个步骤完成一个数据的处理过程,那么从有数据输入的第一个时钟周期开始,直到第4个时钟周期处理完第一个数据,但在以后的每一个时钟周期都会有处理完成的数据输出,流水线设计在开始处理时需要一定的处理时间,但以后就会不断的输出数据,从而大大提高处理速度。(面积换速度)如果不采用流水线设计,那么处理一个数据就需要4个时钟周期,而采用流水线设计则能够提高将近4倍的处理速度

二、 跨时钟域处理

有三种方法

1. 打两拍方法

在进行uart串口通信的学习的过程中,遇到一个不理解的问题,在接收模块中,小梅哥采取的设计方式是接收进行一步同步化处理,那么为什么要进行同步化处理呢?串口通信的设计,接收的波特率一般是发送波特率的16倍,单bit传输,我的理解是,在发送波特率下的串口数据传输到接收波特率下时,这个过程是跨时钟的,对于小工程而言,不进行同步处理貌似没有什么关系,但是当工程对精度的要求比较强,外界干扰比较大的情况下,我们就必须进行同步化处理,下面我将学习第一种针对单bit的跨时钟域处理方法:打两拍。打两拍的方式,其实就是定义两级寄存器对数据进行延拍。

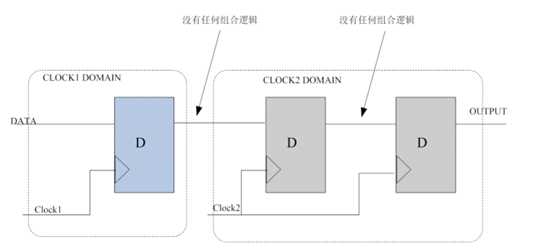

如上图,第一个时钟域将数据发送过来后,在第二个时钟域里用两个D触发器把接收数据进行延拍,中间没有任何组合逻辑。

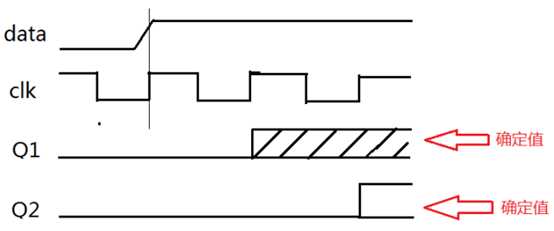

为什么是进行两级延拍呢?从上面的时序图可以看出,data是第一个时钟域的数据,Q1,Q2是第二个时钟域的触发器,在同一个clk时钟下,假设当clk的上升沿来临时,刚好采集到的数据是data的跳变沿(因为数据在有0变为1的时候,显然不是垂直上去的,它有一个建立时间,所以clk的上升沿采集到跳变沿的情况是完全有可能的),这样的话Q1接收的数据会处于亚稳态,但是我们至少可以保证,在clk下一个上升沿,data是稳定的,Q1基本上可以满足第二级寄存器的保持时间和建立时间的要求,出现亚稳态的几率会得到很大的改善。如果多加寄存器进行延拍,只是对Q2的数据进行了延拍,并没有什么意义,所以,我们选择进行两级延拍来处理单bit数据的跨时钟域处理。

三、 一个让我纠结了几个月问题

一个让我纠结了几个月问题

Altera的板子按键按下去时0.不按下去是1,

Altera的板子按键按下去时0.不按下去是1,

Altera的板子按键按下去时0.不按下去是1,

重要的纠结说三遍

Xilinx的板子按下去时1,不按是0

标签:串口通信 方法 back 数据 时钟 问题 需要 比较 logs

原文地址:http://www.cnblogs.com/ninghechuan/p/6970750.html