标签:流水线 集成 避免 遇到 ges 很多 变化 优劣 应该

Verilog是一种硬件描述语言.它是一种描述型工具, 就像素描笔一样,画了一个太阳 。通过这个画,其实我是想告诉大家: 今天太热了!

每次提到Verilog怎么学,总有很多人告诉你, 它是描述型语言,语法简单,你应该去学数字电路设计.

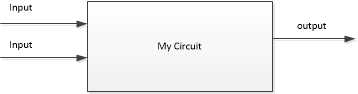

什么叫数字电路 ? 本质肯定是电路, 那电路是干啥用的,肯定是为了实现一个功能的吧。 怎么才能叫实现功能 ? 看下图 :

给电路一定的输入信号,经过我的模块Black_Box,我送出你想要的输出信号。这就实现了功能.

(1) 好了,怎么正确的描述这个电路的呢 ?

------ 这是Verilog语言及风格所要做的事. 什么样的电路可以综合?什么样的语法容易出现疏漏歧义。

(2) 我写的Verilog很复杂、乱哄哄,总觉得有简单的写法

------- 这需要你深刻理解电路细节,用一点Verilog技巧,熟练使用状态机、模块化复用。

(3) 我写的Verilog,可能在某些输入信号条件下,工作的不稳定。

------- 这需要你对异步复位\时钟切换\异步处理\FIFO控制\突发burst\等容易诱发电路故障的原因做到心中有数

然后在电路设计过程中,尽量的去避免这些事件的发生.

这就需要你懂得 :毛刺根源的哪?异步处理怎么才算安全、异步\同步复位优劣、FIFO满写空度?

(4) 你的Verilog,在很多输入条件下都达到稳定了,怎么写才能面积小 ?

-------- 这就要你懂得,怎么去共享乘法器,加法器. 时分复用

(4) 你的Verilog要怎么写才能跑的?

-------- 这就要你懂得, 什么是流水线,怎么适当的插入pipeline.

(5) 你的Verilog要怎么写才能跑,面积又小,又稳定的?

--------- 这就是我们工程师所要做的事。我们只有上面所有的都掌握了,才能算合格的IC前端设计工程师。

其实,最本质的东西: 你要描述一个什么功能 ? 比如实现某种数学运算? 实现某种协议 ?

它们从本质上,都是 输入--->输出的映射 。 时刻保证输出是正确的的输出.

举一个例子:实现UART协议 。 输入信号是:data、rate、len、parity_en,Rx, 输出怎要保证:在正确的时间,

按照正确的速率、发送正确的data、附带正确的parity位+Stop位. 于此同时存下接受的数据。

这就是整个UART模块所要实现的功能,下面就交由你去具体的实现.

(1) 首先我们先保证 时间正确,通过计数器产生pulse、严格卡好时间。

(2) 把 start位+data+parity位+Stop位 按照节拍发送出去。

(3) 于此同时,接受数据,并存入内部mem

(4) 完成所有操作后,UART恢复至IDLE状态。

以上只是简单的描述:中间就涉及到: UART收发状态切换、mem读取写入、数据parity校验等内容。

我们要做的是: 深入理解功能需求,划分成小模块----那么每一个小模块都考虑仔细了,最后把它们集成起来。

如果我们要做的是 数学运算,如DCT变化. 里面有很多乘法,怎么优化共享? 变乘法为加法? 怎么能跑快?怎么插入pipeline?

乘法怎么实现好?是查表?还是直接使用乘法器?这些都是 数字电路设计用经常遇到的问题.

所以,为了更好的实现某个功能, 我们最终会细化成许多小模块, 这些小模块的功能都相对简单很多了, 都是我们熟悉的模块.

我们就能把注意力转移到: 怎么写Verilog能面积又小、速度又快、模块又稳定、coding又整洁易读。

所以学习Verilog : 首先要掌握语法?怎么写不能综合? 怎么容易疏忽、发生歧义? -----保证综合不出错.

其次是电路不稳定一般在什么情况下不稳定?怎么解决? -----保证功能不出错.

再次是怎么写才整洁 ? -----保证逻辑清晰.易维护

最后才是怎么写速度快?怎么写面积小 ? -----保证面积\性能达标

标签:流水线 集成 避免 遇到 ges 很多 变化 优劣 应该

原文地址:http://www.cnblogs.com/mokang0421/p/7533233.html