标签:长按 oat entry images amp 正方形 data height col

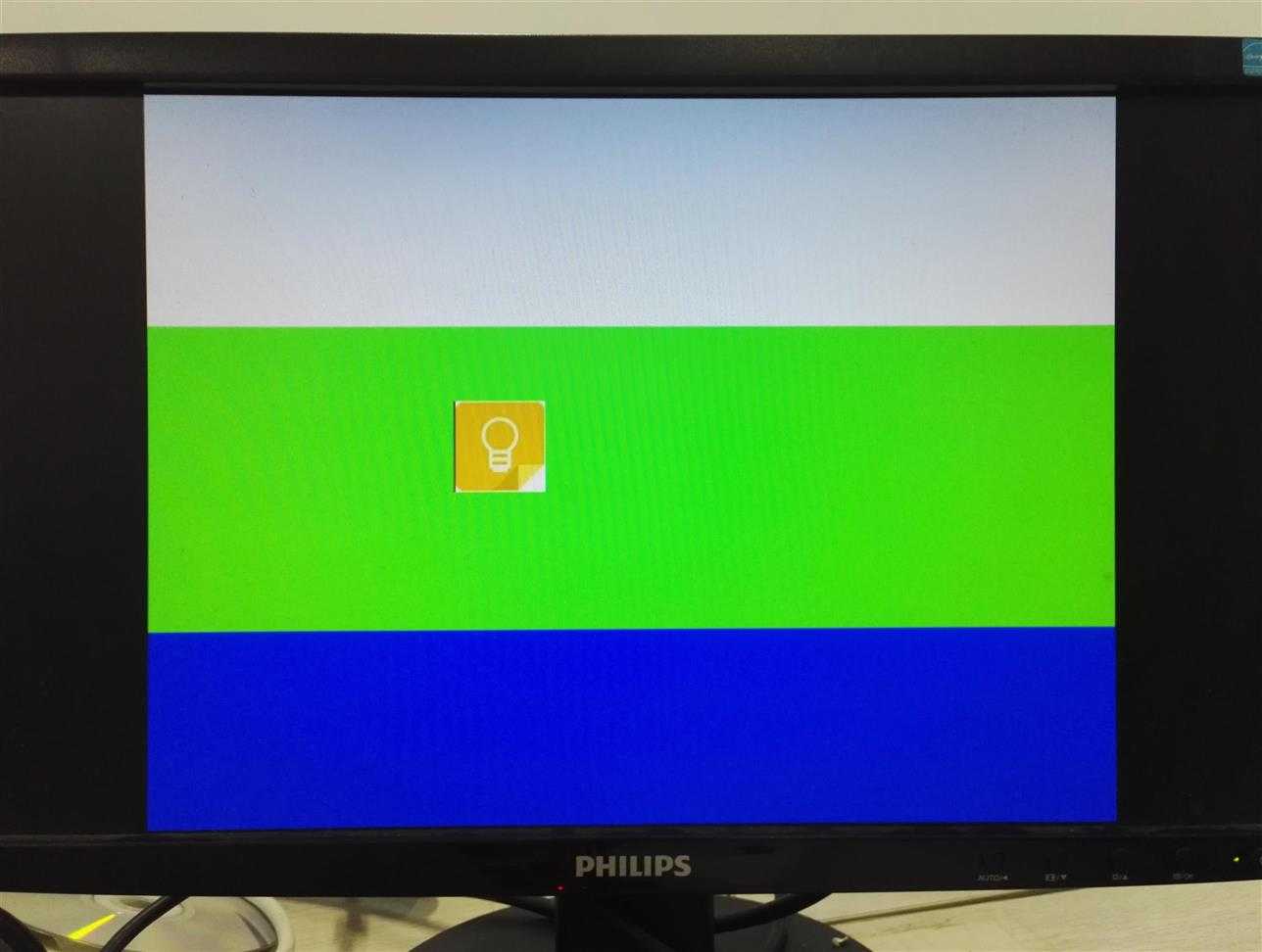

学习VGA显示图片的过程中,遇到了一个小问题,我在显示屏上开了一个60x60的框,放了一张图片进去显示,但是最终的结果如下图所示。

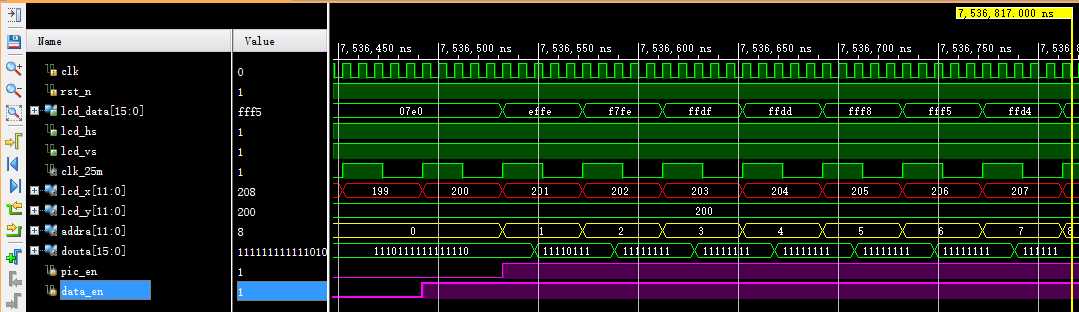

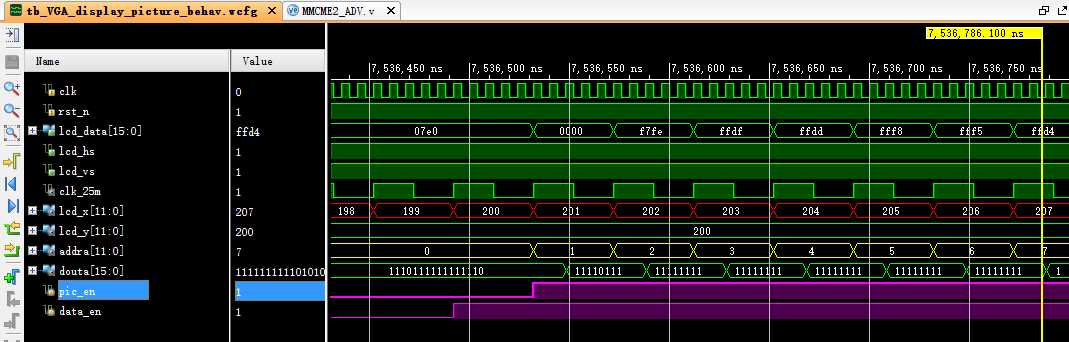

出现了一个竖黑边,看了看代码,分析了一下逻辑没问题,然而看这个显示那肯定是有问题的,然后仿真了一下看看,时序图如下。

正确的时序

错误的时序

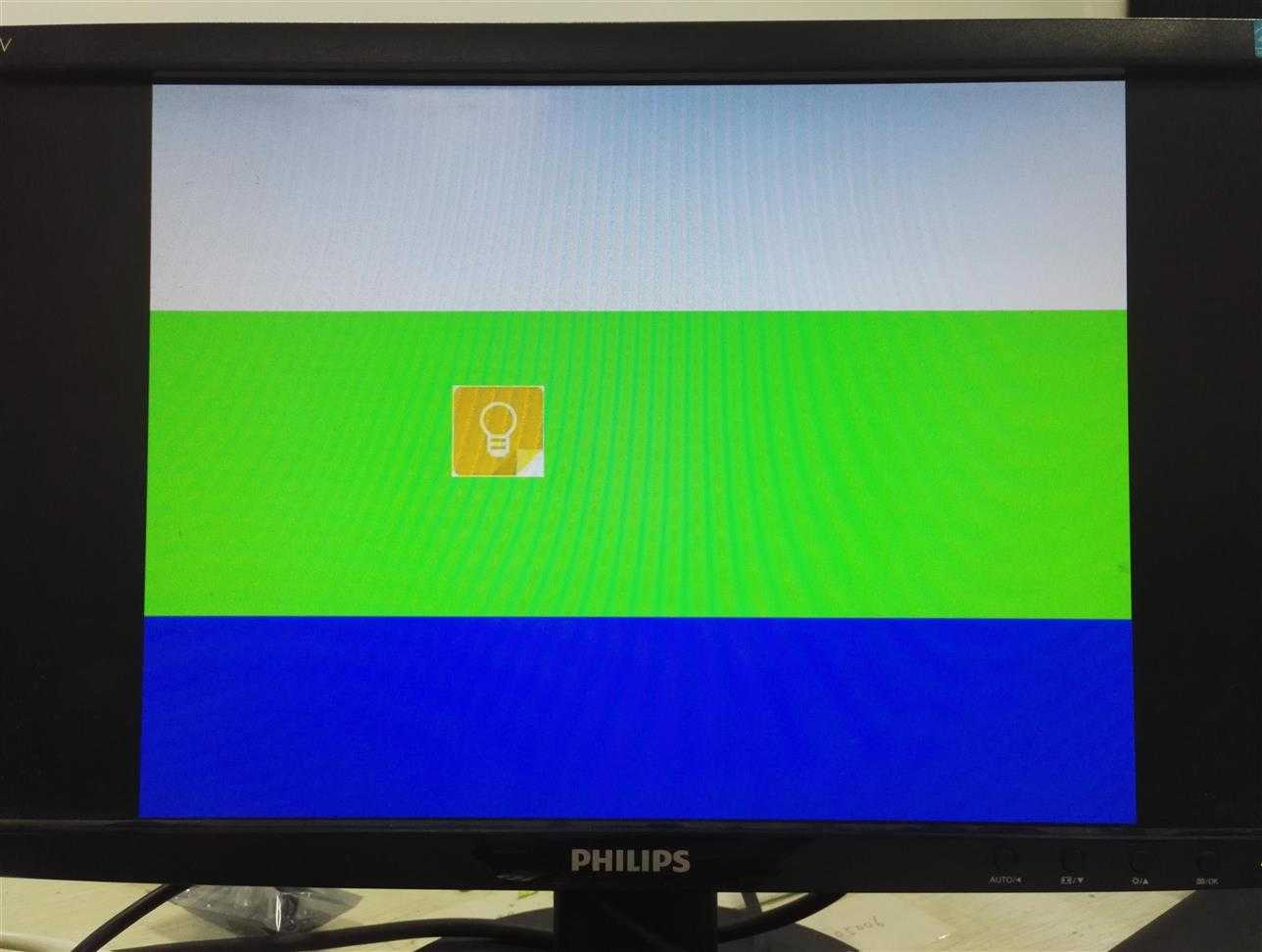

我这是的是当行计数器记到200和场计数器记到200的时候显示ROM中的数据,在显示屏中开出一个60x60的正方形显示区域,对比上两幅图可得,第二幅图在当行计数器计数到200的时候lcd_data本应该是ROM里的数据,但是却输出的是16’h00,这是因为我原始的代码写的是当行计数器记到200的时候给ROM地址加1,然后有个使能信号将ROM的输出读出,但是实际上行计数记到200的同时ROM地址已经加1,那么ROM的第一个数据就没法读出来,然后从第二个数据开始显示,即每一行的第一个数据都没有给出所以最终会显示出一个竖黑边,那么这个问题怎么解决呢?很简单,就是在行计数器记到199的时候给使能信号,所以当显示屏显示第200个数据的时候,ROM的第一个数据正好读出,代码如下:显示结果如下

1 //--------------------------------------------- 2 //addra 3 always @(posedge clk or negedge rst_n)begin 4 if(!rst_n) 5 addra <= 16‘d0; 6 else if(addra == 3600 - 1‘b1) 7 addra <= 16‘d0; 8 else if(lcd_x >= 200 && lcd_x < 260 && lcd_y >= 200 && lcd_y < 260) 9 addra <= addra + 1‘b1; 10 else 11 addra <= addra; 12 end 13 14 //----------------------------------------------------------------------- 15 //pic_en 16 reg pic_en; 17 always @(posedge clk or negedge rst_n)begin 18 if(!rst_n) 19 pic_en <= 1‘b0; 20 else if(lcd_x >= 200 && lcd_x < 260 && lcd_y >= 200 && lcd_y < 260) 21 pic_en <= 1‘b1; 22 else 23 pic_en <= 1‘b0; 24 end 25 26 //----------------------------------------------------------------------- 27 //data_en 28 reg data_en; 29 always @(posedge clk or negedge rst_n)begin 30 if(!rst_n) 31 data_en <= 1‘b0; 32 else if(lcd_x >= 199 && lcd_x < 259 && lcd_y >= 200 && lcd_y < 260) 33 data_en <= 1‘b1; 34 else 35 data_en <= 1‘b0; 36 end 37 38 //lcd_data 39 reg [15:0] lcd_data_r0; 40 reg [15:0] lcd_data_r1; 41 42 always @(posedge clk or negedge rst_n)begin 43 if(!rst_n) 44 lcd_data_r0 <= 16‘b0; 45 else if(lcd_y > 0 && lcd_y <= 150) 46 lcd_data_r0 <= `WHITE; 47 else if(lcd_y > 150 && lcd_y <= 350) 48 lcd_data_r0 <= `GREEN; 49 else if(lcd_y > 350 && lcd_y <= 480) 50 lcd_data_r0 <= `BLUE; 51 else 52 lcd_data_r0 <= 16‘b0; 53 end 54 55 always @(posedge clk or negedge rst_n)begin 56 if(!rst_n) 57 lcd_data_r1 <= 16‘b0; 58 else if(pic_en == 1‘b1) 59 lcd_data_r1 <= douta; 60 else 61 lcd_data_r1 <= 16‘b0; 62 end 63 64 //assign lcd_data = (pic_en == 1‘b1)? `CYAN: lcd_data_r0;//开出一个紫颜色的框 65 66 assign lcd_data = (pic_en == 1‘b1)? lcd_data_r1: lcd_data_r0;

转载请注明出处:NingHeChuan(宁河川)

个人微信订阅号:开源FPGANingHeChuan

如果你想及时收到个人撰写的博文推送,可以扫描左边二维码(或者长按识别二维码)关注个人微信订阅号

知乎ID:NingHeChuan

微博ID:NingHeChuan

原文地址:http://www.cnblogs.com/ninghechuan/p/7577224.html

标签:长按 oat entry images amp 正方形 data height col

原文地址:http://www.cnblogs.com/ninghechuan/p/7577224.html