标签:自我评价 为什么 代码托管 执行 程序 情况 工程师 一个 分段

- 理解虚拟存储器的概念和作用

- 理解地址翻译的概念

- 理解存储器映射

- 掌握动态存储器分配的方法

- 理解垃圾收集的概念

- 了解C语言中与存储器有关的错误

将主存看作是一个存储在磁盘上的地址空间的高速缓存,在主存中只保护活动的区域,并根据需要在磁盘和主存之间来回传送数据;

保护了每个进程的地址空间不被其它进程破坏。

虚拟存储器是强大的

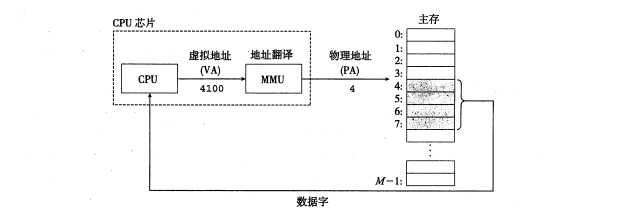

使用虚拟寻址时,CPU通过生成一个虚拟地址VA来访问主存,这个虚拟地址在被送到存储器之前先转换成适当的物理地址,相关硬件为存储器管理单元MMU。

不命中处罚很大

是全相联的——任何虚拟页都可以放在任何的物理页中。

替换算法精密

总是使用写回而不是直写。

页表:是一个数据结构,存放在物理存储器中,将虚拟页映射到物理页,就是一个页表条目的数组。

页表就是一个页表条目PTE的数组。

PTE:由一个有效位和一个n位地址字段组成的,表明了该虚拟页是否被缓存在DRAM中。 页表的组成:有效位+n位地址字段

如果设置了有效位

地址字段表示DRAM中相应的物理页的起始位置,这个物理页中缓存了该虚拟页。

如果没有设置有效位:

空地址:表示该虚拟页未被分配

不是空地址:这个地址指向该虚拟页在磁盘上的起始位置。

颠簸:工作集大小超出了物理存储器的大小。

简化存储器分配:虚拟存储器为向用户进程提供一个简单的分配额外存储器的机制。

WRITE:写权限

外部碎片:发生在当空闲存储器合计起来足够满足一个分配请求,但是没有一个单独的空间块足以处理这个请求时发生

难以量化,不可预测。

问题1解决方案:操作系统开启分页后,每个进程有自己独立的页目录与页表,cpu操作内存会自动将当前线性地址转换为物理地址(MMU负责),然后再放在地址总线上。所以每个进程即使访问相同的线性地址会最终对应到不同的物理地址,因为他们的pde与pte不同。

问题2:内部碎片和外部碎片的区别是什么?

问题2解决方案:要搞清楚内部碎片与外部碎片的区别首先要明白分页与分段

为了有效的利用内存,使内存产生更少的碎片,要对内存分页,内存以页为单位来使用,最后一页往往装不满,于是形成了内部碎片。为了共享要分段,在段的换入换出时形成外部碎片,比如5K的段换出后,有一个4k的段进来放到原来5k的地方,于是形成1k的外部碎片。

(statistics.sh脚本的运行结果截图)

D .

当程序访问大小为2的幂的数组时,直接映射高带缓存中常发生冲突不命中

正确答案: A C D 你的答案: A B

Image 4.png

A .

第三行S为1

B .

第一行t为24

C .

第二行b为5

D .

第三行s的值为0

正确答案: A C D 你的答案: A D

1 #define N 1000

2 3

typedef struct {

4 int vel[3];

5 int acc[3];

6 } point;

7 8

point p[N];

A .

1 void clear1(point p, int n)

2 {

3 int i, j;

4 5

for (i = 0; i < n; i++) {

6 for (j = 0; j < 3; j++)

7 p[i].vel[j] = 0;

8 for (j = 0; j < 3; j++)

9 p[i].acc[j] = 0;

10 }

11 }

B .

1 void clear2(point p, int n)

2 {

3 int i, j;

4 5

for (i = 0; i < n; i++) {

6 for (j = 0; j < 3; j++) {

7 p[i].vel[j] = 0;

8 p[i].acc[j] = 0;

9 }

10 }

11 }

C .

1 void clear3(point *p, int n)

2 {

3 int i, j;

4 5

for (j = 0; j < 3; j++) {

6 for (i = 0; i < n; i++)

7 p[i].vel[j] = 0;

8 for (i = 0; i < n; i++)

9 p[i].acc[j] = 0;

10 }

11 }

D .

不确定

正确答案: C 你的答案: B

程序中()语句具有良好的局部性

A .

顺序

B .

分支

C .

循环

D .

以上都是

正确答案: C 你的答案: A

有关局部性原理,说法正确的是()

A .

程序访问一个向量,步长越小或短,空间局部性越好

B .

局部性有两种形式:空间局部性,时间局部性

C .

程序访问一个向量,步长越大空间局部性越好。

D .

硬件、OS,应用程序都会用到局部性原理

正确答案: A B D 你的答案: A B

下面说法正确的是()

A .

CPU通过内存映射I/O向I/O设备发命令

B .

DMA传送不需要CPU的干涉

C .

SSD是一种基于闪存或Flash的存储技术

D .

逻辑磁盘块的逻辑块号可以翻译成一个(盘面,磁道,扇区 )三元组。

下面()是I/O总线

A .

USB

B .

PCI

C .

网卡

D .

图形卡

正确答案: B 你的答案: A

有关磁盘操作,说法正确的是()

A .

对磁盘扇区的访问时间包括三个部分中,传送时间最小。

B .

磁盘以字节为单位读写数据

C .

磁盘以扇区为单位读写数据

D .

读写头总处于同一柱面

正确答案: A C 你的答案: C D

计算下面磁盘的容量():4个盘片,100000个柱面,每条磁道400个扇区,每个扇区512个字节

A .

81.92GB

B .

40.96GB

C .

163.84

D .

327.68GB

正确答案: C 你的答案: A

根据携带信号不同,总线可分为()

A .

系统总线

B .

数据总线

C .

内存总线

D .

地址总线

E .

控制总线

正确答案: B D E 你的答案: A C

- [20155232](http://www.cnblogs.com/lsqsjsj/p/7769029.html)| 代码行数(新增/累积) | 博客量(新增/累积) | 学习时间(新增/累积) | 重要成长 | |

|---|---|---|---|---|

| 目标 | 5000行 | 30篇 | 400小时 |

| 第四周 | 300/1300 | 2/9 | 30/90 | |

尝试一下记录「计划学习时间」和「实际学习时间」,到期末看看能不能改进自己的计划能力。这个工作学习中很重要,也很有用。

耗时估计的公式

:Y=X+X/N ,Y=X-X/N,训练次数多了,X、Y就接近了。

计划学习时间:XX小时

实际学习时间:XX小时

改进情况:

(有空多看看现代软件工程 课件

软件工程师能力自我评价表)

2017-2018-1 20155215 《信息安全系统设计基础》第11周学习总结

标签:自我评价 为什么 代码托管 执行 程序 情况 工程师 一个 分段

原文地址:http://www.cnblogs.com/xuanyan/p/7967504.html