标签:ima ttl 分享图片 除了 电路 部分 自动 under 影响

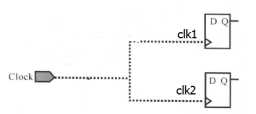

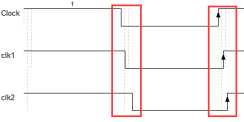

①时钟的偏移(skew):时钟分支信号在到达寄存器的时钟端口过程中,都存在有线网等延时,由于延时,到达寄存器时钟端口的时钟信号存在有相位差,也就是不能保证每一个沿都对齐,这种差异称为时钟偏移(clock skew),也叫时钟偏斜。时钟的偏移如下图所示:

此外,时钟skew与时钟频率并没有直接关系,skew与时钟线的长度及被时钟线驱动的时序单元的负载电容、个数有关。

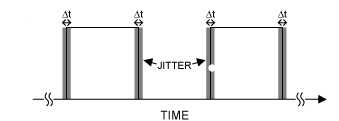

②时钟抖动(jitter):相对于理想时钟沿实际时钟存在不随时间积累的、时而超前、时而滞后的偏移称为时钟抖动,简称抖动,如下图所示:

时钟的抖动可以分为随机抖动(Random Jitter,简称Rj)和固有抖动(Deterministic jitter):

随机抖动的来源为热噪声、Shot Noise和Flick Noise,与电子器件和半导体器件的电子和空穴特性有关,比如ECL工艺的PLL比TTL和CMOS工艺的PLL有更小的随机抖动;

固定抖动的来源为:开关电源噪声、串扰、电磁干扰等等,与电路的设计有关,可以通过优化设计来改善,比如选择合适的电源滤波方案、合理的PCB布局和布线。

也就是说:jitter与时钟频率无直接关系。

时钟的偏移和时钟的抖动都影响着时钟网络分枝的延迟差异(相位差异),在Design Compiler里面,我们用时钟的不确定性(uncertainty)来表示这两种情况的影响。

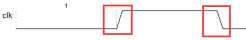

③时钟的转换时间(transition) :时钟的上升沿跳变到下降沿或者时钟下降沿跳变到上升沿的时间,这个时间并不是如左下图所示那样完全没有跳变时钟的,而是像右下图那样,时钟沿的跳变时间就是时钟的转换时间(后面约束的时候会有相关的解释)。

理想:

带转换时间的时钟:

时钟的转换时间与与单元的延时时间(也就是器件特性)还有电容负载有关。

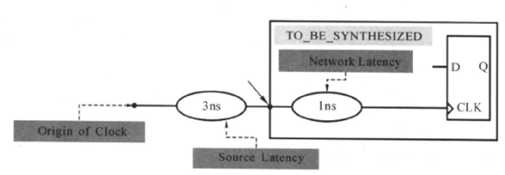

④时钟的延时(latency) :时钟从时钟源(比如说晶振)出发到达触发器时钟端口的延时,称为时钟的延时,包含时钟源延迟(source latency)和时钟网络的延迟(network latency),如下图所示:

时钟源延迟(clock source latency),也称为插入延迟(insertion delay),是时钟信号从其实际时钟原点到设计中时钟定义点(时钟的输入引脚)的传输时间,上图是3ns。

时钟网络的延迟( clock network latency)是时钟信号从其定义的点(端口或引脚)到寄存器时钟引脚的传输,经过缓冲器和连线产生的延迟(latency),上图是1ns。

Clock gating and PLL

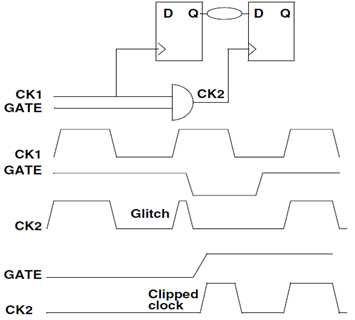

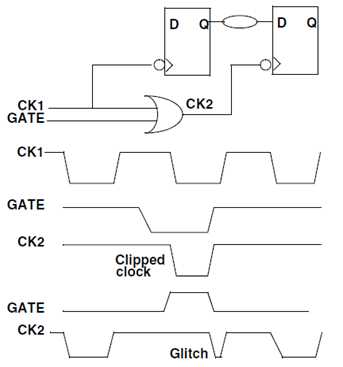

一个gating的clock是指:clock network除了包含inverter和buffer外,还有其他logic。

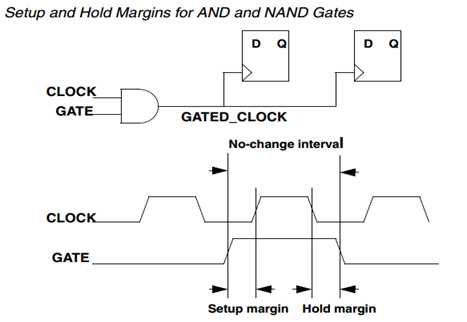

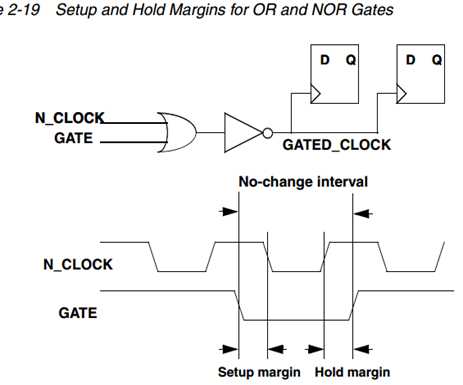

PrimeTime会自动的对gating input进行setup和hold violation的检查,来防止clock不被interrupt和clipped

(在该情况下,combinational gates,一个signal是clock并且通过该gate进行propagation,另一个signal是不是clock)

命令set_clock_gating_check可以设置指定cell/pin的clock gating check

set_clock_gating_check -setup 0.2 -hold 0.4 [get-clocks CLK1]

setup check保证:control data signal在clock active之前进行enable。

hold check保证:control data signal保持stable直到clock inactive

check准则不变,在clock gating的cell不一致时,检查的部分也会不一样。

在AND逻辑下,保证clock的高电平完整

在OR-INV逻辑下,保证clock的低电平完整

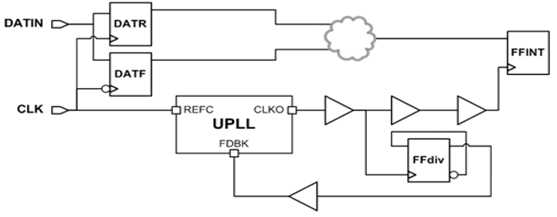

PT中对于PLL的timing check

PLL通过调整feedback和reference clock的phase,来减小launch/capture clock的clock skew

PrimeTime通过在library中指定reference clock pin, output pin, feedback pin来进行PLL cell的analysis。

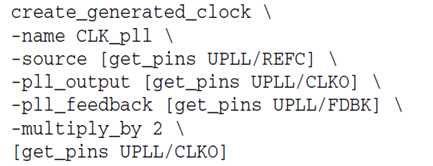

通过命令create_generated_clock来定义PLL-generated clock

分别用-pll_reference/-pll_output/-pll_feedback来指定三个pin

可以通过-pll_shift来调整early/late latency of the generated clock

PLL的SDC定义中,还必须进行CRPR的calculatio

标签:ima ttl 分享图片 除了 电路 部分 自动 under 影响

原文地址:https://www.cnblogs.com/YLuluuu/p/9009694.html