标签:jta divide 调试 VID debug 处理器 多处理器 except 经典

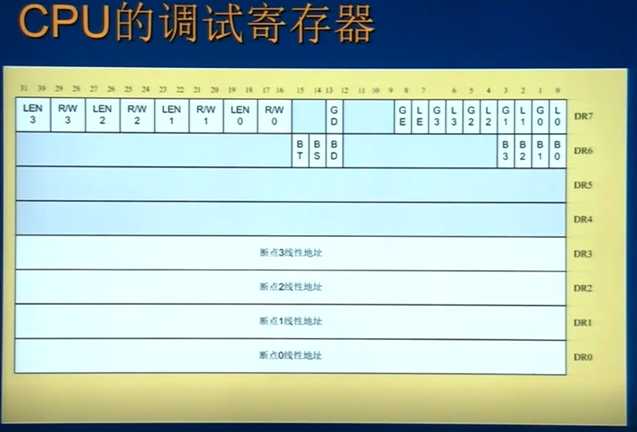

R/W 0 和LEN 0对应断点0线性地址;

DR则是调试寄存器

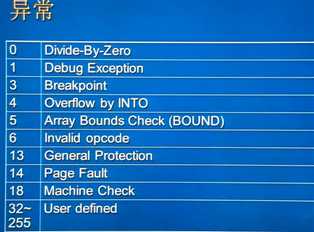

比如说INT 3 (CC)断点最终会调用 3Breakpoint

单步执行则是 1号表Debug Exception

代码除0则触发 0号表Divide-By-Zero

标签:jta divide 调试 VID debug 处理器 多处理器 except 经典

原文地址:https://www.cnblogs.com/hanhandaren/p/11172973.html