标签:override data cloc lis clock esc err dep ssi

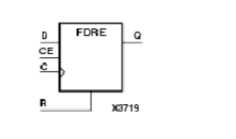

1、源语---FDRE

FDRE代表一个单D型触发器,含的有五个信号分别为: 数据(data,D)、时钟使能(Clock enable,CE)、时钟(Clock)、同步复位(synchronous reset,R)、数据输出(dataout,Q)。当输入的同步复位信号为高时,否决(override)所有输入,并在时钟的上升沿将输出Q为低信号。在时钟的上升沿数据被加载进入D触发器的输入。

FDRE #( .INIT (INITIALISE[0]) ) data_sync_reg1 ( .C (clk), // 同步时钟 .D (data_sync0), //异步数据输入 .Q (data_sync1), //同步数据输出 .CE (1‘b1), //时钟使能信号 .R (1‘b0) //复位信号输入,高电平有效 );

由于数据可能与时钟存在着不同步的情况,尤其是在对同步精度要求高的场合,一般还是用多次FDRE源语使得数据、控制信号等同步,例如在一个三态网数据同步模块中使用了四个D触发器进行数据同步:

`timescale 1ps / 1ps (* dont_touch = "yes" *) module tri_mode_ethernet_mac_0_sync_block #( parameter INITIALISE = 1‘b0, parameter DEPTH = 5 ) ( input clk, // clock to be sync‘ed to input data_in, // Data to be ‘synced‘ output data_out // synced data ); // Internal Signals wire data_sync0; wire data_sync1; wire data_sync2; wire data_sync3; wire data_sync4; (* ASYNC_REG = "TRUE", SHREG_EXTRACT = "NO" *) FDRE #( .INIT (INITIALISE[0]) ) data_sync_reg0 ( .C (clk), .D (data_in), .Q (data_sync0), .CE (1‘b1), .R (1‘b0) ); (* ASYNC_REG = "TRUE", SHREG_EXTRACT = "NO" *) FDRE #( .INIT (INITIALISE[0]) ) data_sync_reg1 ( .C (clk), .D (data_sync0), .Q (data_sync1), .CE (1‘b1), .R (1‘b0) ); (* ASYNC_REG = "TRUE", SHREG_EXTRACT = "NO" *) FDRE #( .INIT (INITIALISE[0]) ) data_sync_reg2 ( .C (clk), .D (data_sync1), .Q (data_sync2), .CE (1‘b1), .R (1‘b0) ); (* ASYNC_REG = "TRUE", SHREG_EXTRACT = "NO" *) FDRE #( .INIT (INITIALISE[0]) ) data_sync_reg3 ( .C (clk), .D (data_sync2), .Q (data_sync3), .CE (1‘b1), .R (1‘b0) ); (* ASYNC_REG = "TRUE", SHREG_EXTRACT = "NO" *) FDRE #( .INIT (INITIALISE[0]) ) data_sync_reg4 ( .C (clk), .D (data_sync3), .Q (data_sync4), .CE (1‘b1), .R (1‘b0) ); assign data_out = data_sync4; endmodule

标签:override data cloc lis clock esc err dep ssi

原文地址:https://www.cnblogs.com/luxinshuo/p/11913988.html