标签:func mic tap 数字电路 etl mamicode UNC 基于 异或

一、基于standcell的ASIC设计流程??所谓standcell library即为标准单元库,主要指数字电路,反相器,与非门,或非门,异或门,施密特触发器之类的 基本元器件。

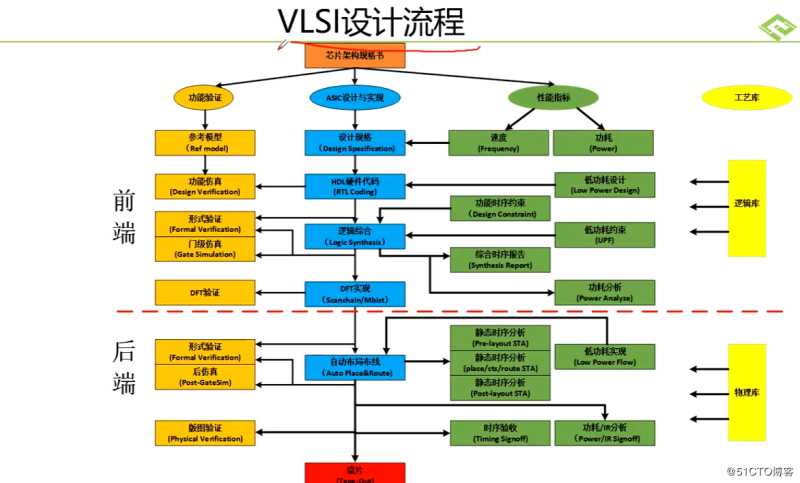

设计流程为:

?算法模型(C/C++/Matlab)--->RTL HDL VHDL/Verilog--->NetlistVerilog--->Layout GDSII--->Tape-Out

standcell library包含:NetlistVerilog和Layout GDSII

RTL HDL VHDL/Verilog--->NetlistVerilog 逻辑综合工具根据基本单元库的功能-时序模型,将行为级代码翻译成具体的电路实现结构

Netlist Verilog--->Layout GDSII 布局布线工具根据基本单元库的时序-几何模型,将电路单元布局布线成实际电路板图

Layout GDSII--->Tape-Out 对功能,时序,制造参数进行检查Marketing request -->Architecture Spec.-->Arch/Algorithm Emulation -->Design Spec.-->RTL Coding-->IP Level RTL coding-->IP Level RTL simulation-->Unit/chip Level RTL simulation-->Logic Synthesis(逻辑综合)-->形式验证-->STA(静态时序分析)-->DFT(design for test)-->PR版图生成,自动布局布线-->时钟树插入-->DRC/LVS -->Post layout STA -->生成GDSII

在上面的流程中,工程师职责与使用工具可总结为下表

| 流程 | 工程师 | 工作 | 工具 |

|---|---|---|---|

| Marketing request | - | - | - |

| Architecture Spec. | Architecture engineer | Top atchitect,Project function spec | - |

| Arch/Algorithm Emulation | Algorithm Engineer | - | C/C++/Matlab |

| Design Spec. | - | Design spec example | - |

| RTL Coding | RTL design engineer | - | 使用VHDL/Verilog/System Verilog实现 |

| IP Level RTL coding | - | - | - |

| IP Level RTL coding | IP level verification engineer | IP level verification | Make file;仿真验证工具,Cadence:Incisive,Synopsys:VCS,Mentor:QuestaSim |

| Unit/chip Level RTL simulation | Integrate engineer | Unit/chip level verification(full chip verification engineer) | - |

| Logic Synthesis | ASIC Design Engineer | Gate Level verification | 逻辑综合工具,Cadence:Genus,Synopsys:Design Compiler |

| 形式验证 | ASIC Front-End Design Engineer | - | 形式验证工具,Cadence:Conformal,Synopsys:Formality |

| STA(静态时序分析) | ASIC Front-End Design Engineer | TCL Script | 静态时序分析工具,Cadence:Tempus,Synopsys:Prme Time |

| DFT(design for test) | DFT engineer | 插入可测试链scan chain | - |

| PR版图生成,自动布局布线 | Physical Design Engineer | - | 自动布线工具,Cadence:Innovus,Synopsys:IC Compiler |

| 时钟树插入 | - | - | - |

| DRC/LVS | - | - | 物理验证工具,Cadence:Diva/dracula,Synopsys:Hercules,Mentor:Calibre |

| Post layout STA | - | - | - |

| 生成最终GDSII | - | - | - |

| Tap-Out | - | - | - |

逻辑综合就是把设计实现的RTL代码映射到特定的工艺库,输出成门级网表Netlist

从功能上(STA是时序上)对综合后的网表进行验证。常用的就是等价性检查(Equivalence Check),以功能验证后的HDL设计为参考,对综合后的网表功能,他们是否在功能上存在等价性。

静态时序分析,主要在时序上对电路进行验证,检查电路是否存在建立时间,保持时间的违例前端设计与后端设计

前端设计(RTL to Netlist)

RTL(Register Transfer Level)利用引荐描叙语言对电路以寄存器之间的传输进行描述

逻辑综合:将RTL级设计中所得的程序代码翻译成实际电路的各种元器件以及他们的连接关系,用一张图来表示成为网表(Netlist)

STA(static timing analysis,静态时序分析),套用特定的时序模型,针对电路分析是否违反给定的时序限制

后端设计(Netlist to Layout)

APR(自动布局布线)-->Extract RC(提取延时信息)-->DRC(设计规则检查)-->LVS(版图电路一致性检查)VSLI设计流程

标签:func mic tap 数字电路 etl mamicode UNC 基于 异或

原文地址:https://blog.51cto.com/yinsuifeng/2479989