标签:prefix gis pci cas 级别 reference tin ref 报告

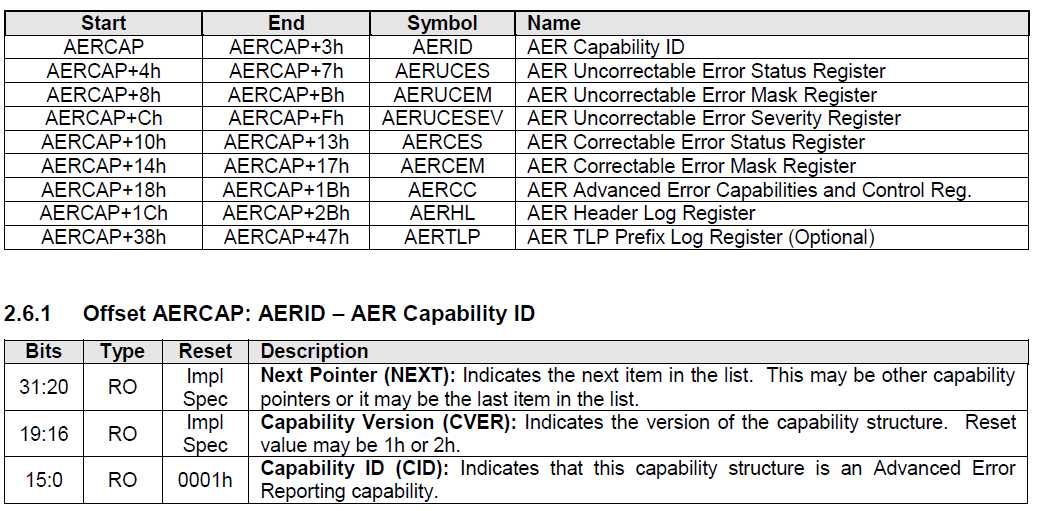

2.6 Advanced Error Reporting Capability (Optional)

The Advanced Error Reporting definitions below are based on the PCI Express 2.1 Base specification. Implementations may choose to base the device on a specification beyond the PCI Express 2.1 Base specification. In all cases, the PCI Express Base specification is the normative reference for the Advanced Error Reporting registers.

2.6高级错误报告功能(可选)

下面的高级错误报告定义基于PCI Express 2.1基本规范。 实施人员可以选择将设备基于PCI Express 2.1 Base规范以外的规范。 在所有情况下,PCI Express Base规范都是Advanced Error Reporting寄存器的规范参考。

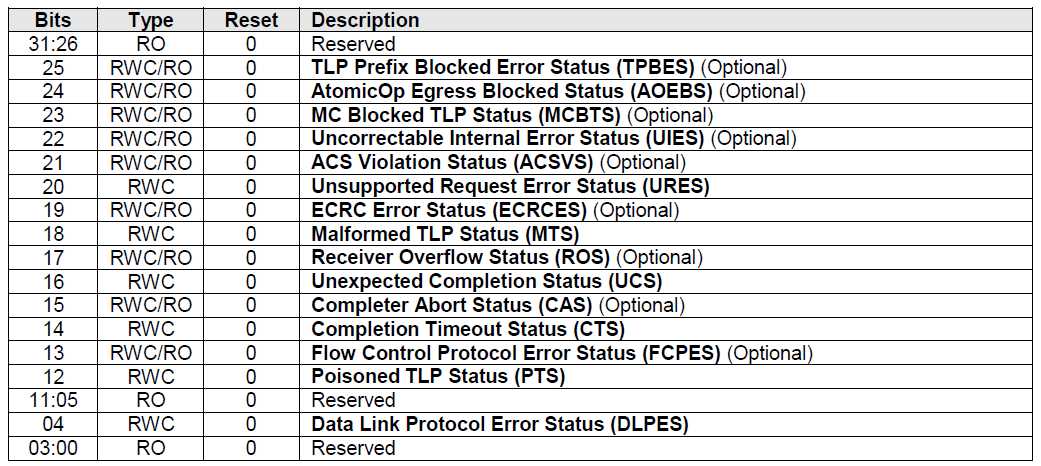

2.6.2 Offset AERCAP + 4: AERUCES – AER Uncorrectable Error Status Register

This register indicates the error detection status of the individual errors on the controller. These bits are sticky – they are neither initialized nor modified during a hot reset or Function Level Reset (FLR).

2.6.2 AERCAP + 4偏移量:AERUCES – AER无法纠正的错误状态寄存器

该寄存器指示控制器上各个错误的错误检测状态。 这些位具有粘性–在热复位或功能级别复位(FLR)期间既不会初始化也不会对其进行修改。

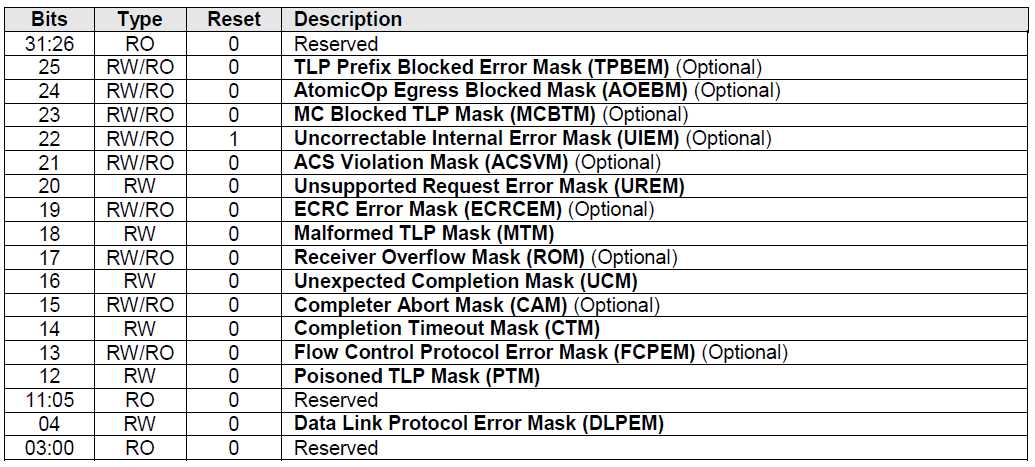

2.6.3 Offset AERCAP + 8: AERUCEM – AER Uncorrectable Error Mask Register

This register controls the reporting of the individual errors by the controller. A masked error is not reported in the Header Log register (AERHL), does not updated the First Error Pointer (AERCC.FEP), and is not reported to the host. These bits are sticky – they are neither initialized nor modified during a hot reset or FLR.

2.6.3偏移量AERCAP + 8:AERUCEM – AER不可校正错误掩码寄存器

该寄存器控制控制器报告单个错误。 在标头日志寄存器(AERHL)中未报告掩蔽的错误,没有更新第一个错误指针(AERCC.FEP),也没有报告给主机。 这些位具有粘性–在热复位或FLR期间既不进行初始化也不进行修改。

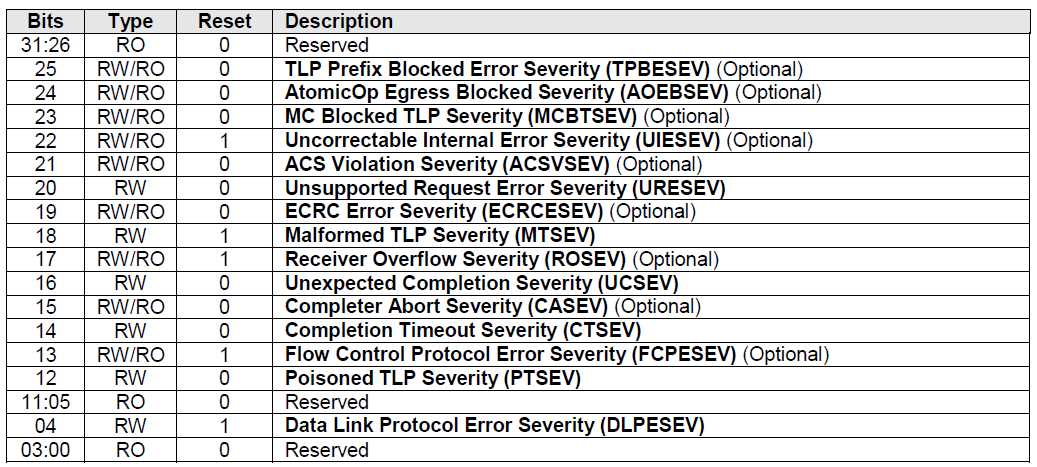

2.6.4 Offset AERCAP + Ch: AERUCESEV – AER Uncorrectable Error Severity Register

This register controls whether an individual error is reported as a non-fatal or a fatal error. An error is reported as fatal when the corresponding error bit in the severity register is set (‘1’). If the bit is cleared (‘0’), the corresponding error is considered non-fatal. These bits are sticky – they are neither initialized nor modified during a hot reset or FLR.

2.6.4偏移量AERCAP +通道:AERUCESEV – AER不可纠正错误严重性寄存器

该寄存器控制将单个错误报告为非致命错误还是致命错误。 当严重性寄存器中的相应错误位被设置为“ 1”时,错误被报告为致命错误。 如果该位被清除(0),则相应的错误被认为是非致命的。 这些位具有粘性–在热复位或FLR期间既不进行初始化也不进行修改。

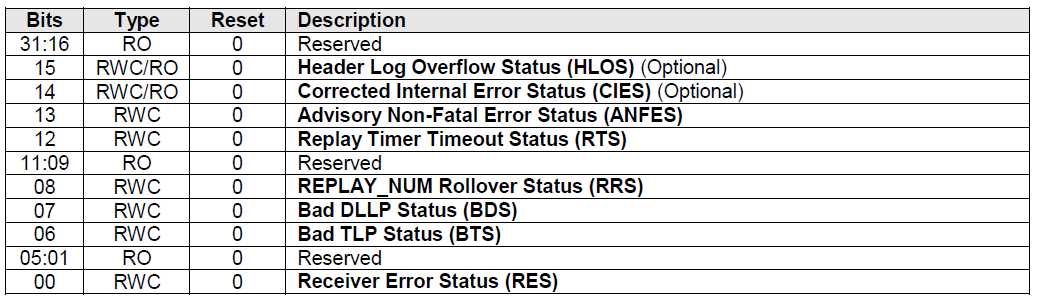

2.6.5 Offset AERCAP + 10h: AERCS – AER Correctable Error Status Register

This register reports error status of individual correctable error sources from the controller. These bits are sticky – they are neither initialized nor modified during a hot reset or FLR.

2.6.5偏移量AERCAP + 10h:AERCS – AER可校正错误状态寄存器

该寄存器报告控制器中各个可纠正错误源的错误状态。 这些位具有粘性–在热复位或FLR期间既不进行初始化也不进行修改。

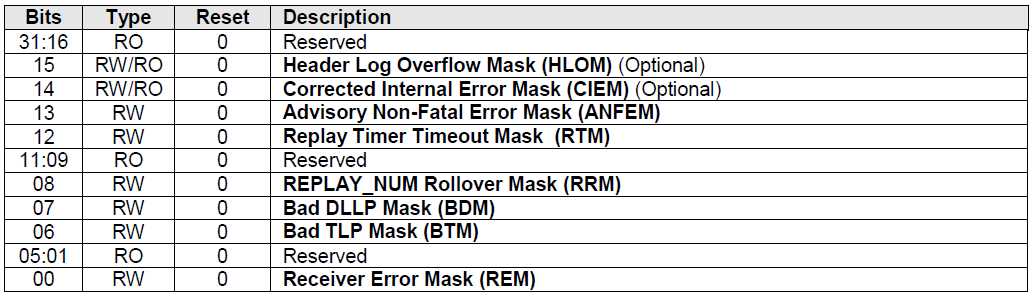

2.6.6 Offset AERCAP + 14h: AERCEM – AER Correctable Error Mask Register

This register controls the reporting of the individual correctable errors by the controller. A masked error is not reported to the host. These bits are sticky – they are neither initialized nor modified during a hot reset or FLR.

2.6.6偏移AERCAP + 14h:AERCEM – AER可校正错误掩码寄存器

该寄存器控制控制器对单个可纠正错误的报告。 屏蔽的错误不会报告给主机。 这些位具有粘性–在热复位或FLR期间既不进行初始化也不进行修改。

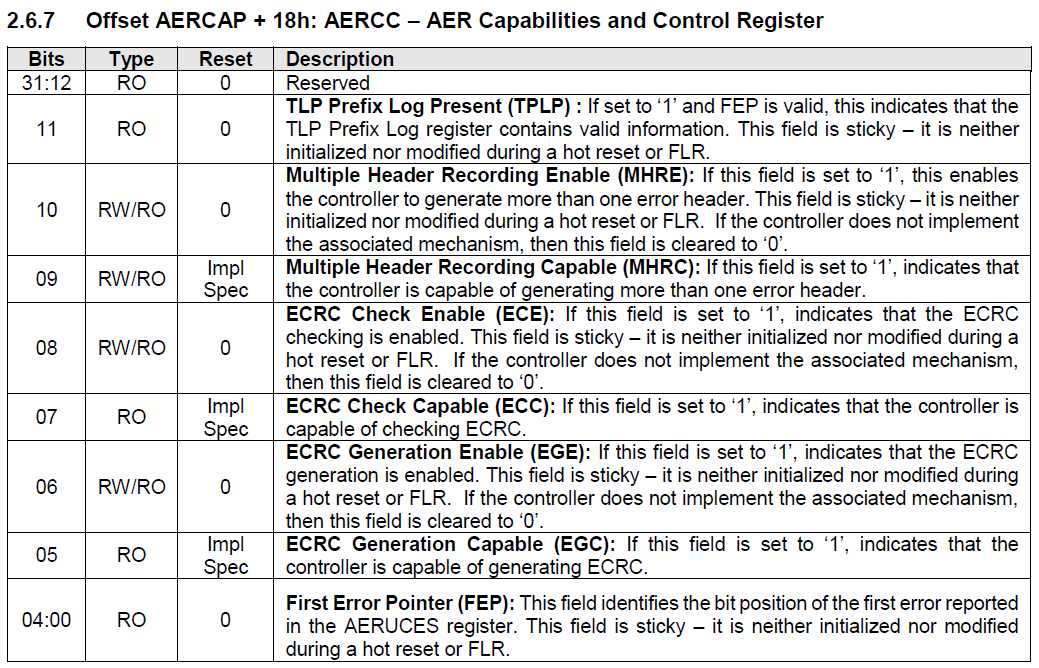

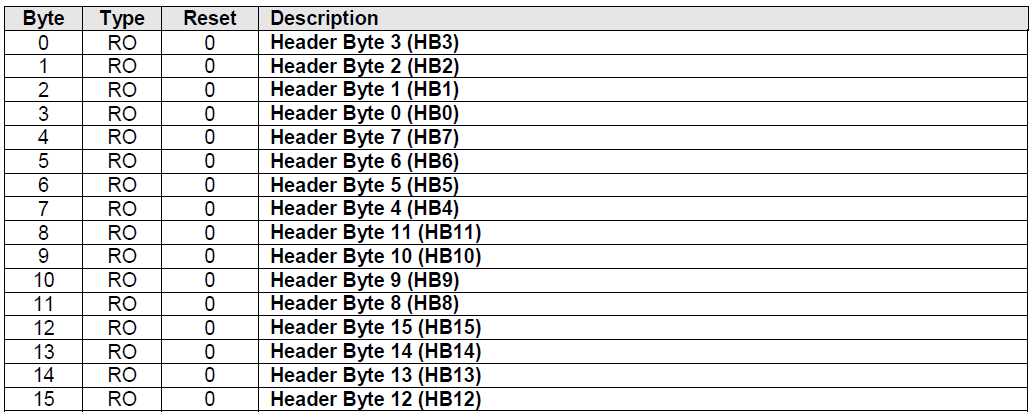

2.6.8 Offset AERCAP + 1Ch: AERHL – AER Header Log Register

This register contains the header for the TLP corresponding to a detected error. This register is sticky – it is neither initialized nor modified during a hot reset or FLR.

2.6.8偏移AERCAP + 1Ch:AERHL – AER标头日志寄存器

该寄存器包含与检测到的错误相对应的TLP的标头。 该寄存器是粘性的–在热复位或FLR期间既不初始化也不修改。

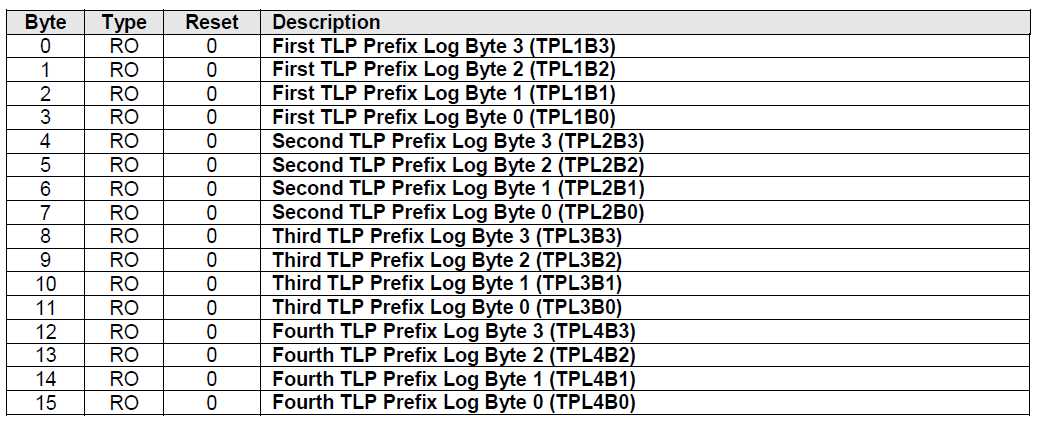

2.6.9 Offset AERCAP + 38h: AERTLP – AER TLP Prefix Log Register (Optional)

This register contains the End-End TLP prefix(es) for the TLP corresponding to a detected error. This register is sticky – it is neither initialized nor modified during a hot reset or FLR.

2.6.9偏移AERCAP + 38h:AERTLP – AER TLP前缀日志寄存器(可选)

该寄存器包含与检测到的错误相对应的TLP的End-End TLP前缀。 该寄存器是粘性的–在热复位或FLR期间既不初始化也不修改。

2.7 Other Capability Pointers

Though not mentioned in this specification, other capability pointers may be necessary, depending upon the implementation. Examples would be the PCI-X capability for PCI-X implementations, and potentially the vendor specific capability pointer.

These capabilities are beyond the scope of this specification.

2.7其他能力指标

尽管在本规范中未提及,但根据实现情况,可能还需要其他功能指针。 示例包括用于PCI-X实现的PCI-X功能,以及潜在的供应商特定功能指针。

这些功能超出了本规范的范围。

2.6 Advanced Error Reporting Capability (Optional)

标签:prefix gis pci cas 级别 reference tin ref 报告

原文地址:https://www.cnblogs.com/hswy/p/12660514.html