标签:一个 实现 还需要 包头 否则 相关 控制 完整 img

最近做的一个项目中,ZYNQ本来有两个网口,eth0通过PS端的IO直接引出去,eth1通过PL的EMIO引出去,ARM端软件实现网络的收发。ARM端实现的功能较多,性能遇到瓶颈,此时还需要ARM软件实现网络发送100MBps/s的数据,单单网络发送部分大概就占用了30%的CPU,最大是CPU占用率达到了90%左右,有点高到不能接受。

研究了开源的三速以太网Verilog实现后,发现MAC层的实现,除了在UDP封包后加入了前导码和CRC校验外,就是流量控制相关的内容,FPGA实现发送TS流不需要考虑流量控制(否则在FPGA内部实现也是溢出导致错误)。于是想到实现简单MAC层的功能,即加入前导码和CRC校验。

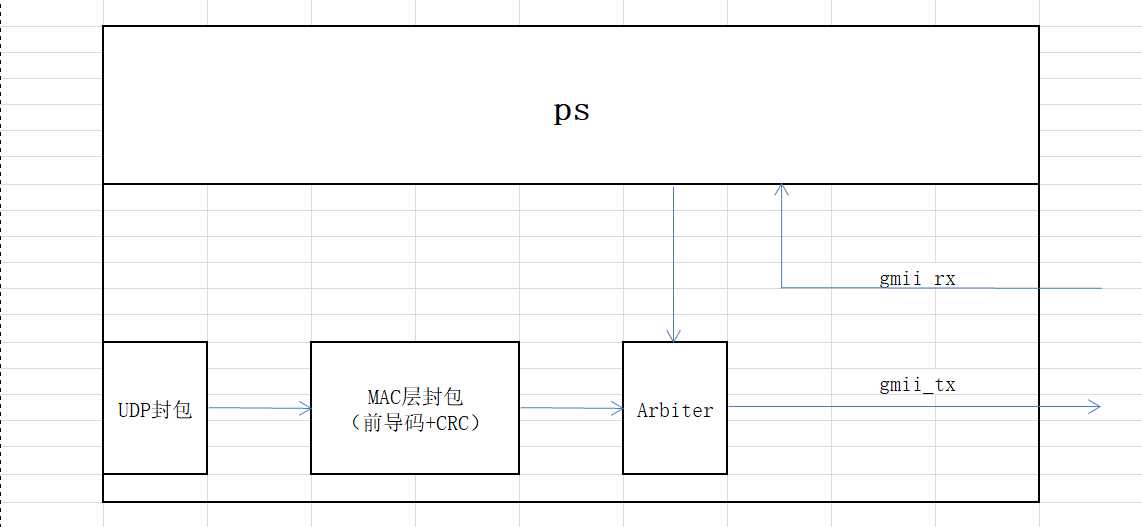

ARM侧MAC发过来的数据时序很有规则,即valid为高时为一个完整的包,valid不会出现一个包内中间变低的情况,因此很好区分包头和包尾,于是做了下图所示的仲裁逻辑,将ARM发送的包和FPGA内部产生的数据包通过分时复用的方式从eth1网口发送出去。

当然这种实现方式缺点也显而易见,由于ARM和FPGA侧的发送的缓冲区都不是很大,因此如果同时过来很多数据包可能导致缓冲区溢出。但是对于当前项目的引用ARM侧是不会发送大量数据的,只有一些IGMP、ARP等报文信息,因此大部分数据都是FPGA侧去发送的,不存在缓冲区溢出的现象,满足功能需求,同时大大降低了ARM的系统负荷,降低CPU占用率大概30%左右。

系统框图如下所示:

标签:一个 实现 还需要 包头 否则 相关 控制 完整 img

原文地址:https://www.cnblogs.com/huakaimanlin/p/12777376.html