标签:diff 假设 code 多路径 就是 不同的 enc 芯片 获得

5.1概述

5.1.1延时计算基础

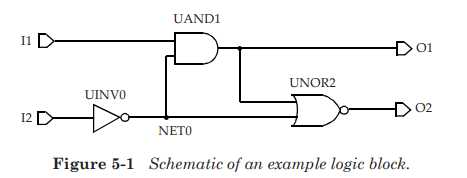

本章不考虑互联线上的电容影响。transition time和slew 本质上一样。对于多输入引脚单元来说,不同的输入引脚引发不同的输出转换时间值。单元延时由输入引脚转换时间和输出负载共同决定。

5.1.2含互联线延时计算

布图之前的时序

正如第四章所介绍的,布图之前互联线寄生电容电阻的大小可以用线负载模型来估计。

布图之后的时序

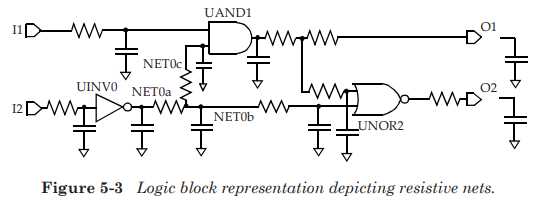

这里注意,在布图后的寄生中包含电阻,这时候原来的查表式的非线性模型就不再适用了,因为变量中没有电阻这一项。

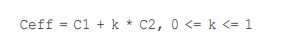

5.2使用有效电容计算单元延时

采用 有效电阻 来处理电阻的影响。

互联线屏蔽效应:近端电容的充电速度 快于 远端电容的充电速度

对于工具来说,获得布图后的延时:工具先通过迭代法计算获得有效电容值。

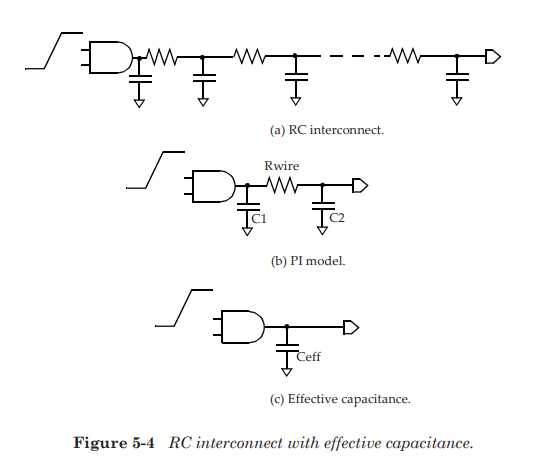

5.3互联延时

RC互联可以是预布局,也可以是后期布局。

基本延时计算将所有电容(包括耦合电容)视为接地电容。

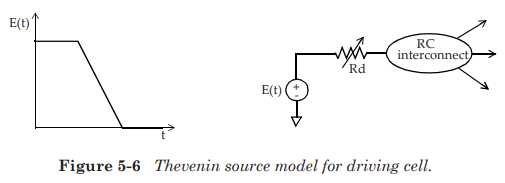

具体计算是,使用戴维宁等效电源:

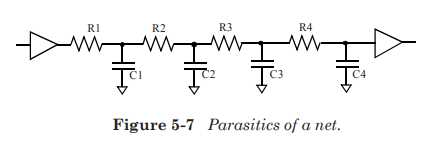

连线上的寄生:

接下来介绍了3种net延时模型:

Elmore Delay适用于RC树、high order interconnect delay Estimation高阶互联线延时估计 提高了精度、full chip delay caculation

5.4 slew 合并

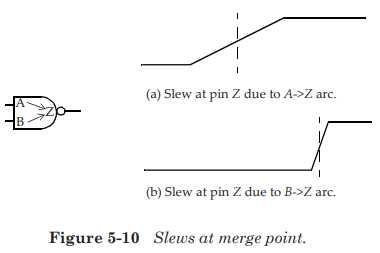

slew merge point:比如下图中的引脚Z

如果两个输入先后引发输出slew,a:慢slew并且到得早,b是快slew并到得晚:

最大路径分析有两可能:(我想这里应该这样考虑:AB只有一个发生翻转,单元延时是电压波形50%处相差的时间)

1.最坏slew传播。图a中的情况。A-Z准确 B-Z悲观

2.最坏arrival传播。图b中的情况。A-Z乐观 B-Z准确

最小路径分析也有两种可能:

1.最好slew传播。图b中的情况。A-Z悲观 B-Z准确

2.最好arrival传播。图b中的情况。A-Z准确 B-Z乐观

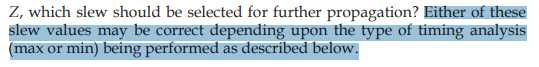

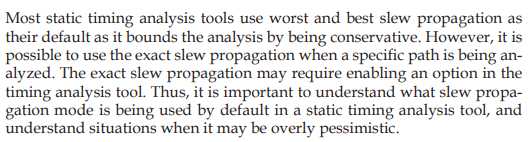

下面这段话看起来很重要:

“大多数的sta工具默认使用最坏和最好的slew传播,因为这两种可能比较保守,给分析划定了边界。然而当对某条精确的路径进行分析时可能会使用精确的slew传播。精确的slew传播可能需要打开工具中的某个操作。因此,知道工具在默认使用哪种slew传播模式并且理解时序过于悲观时的情景,是重要的”

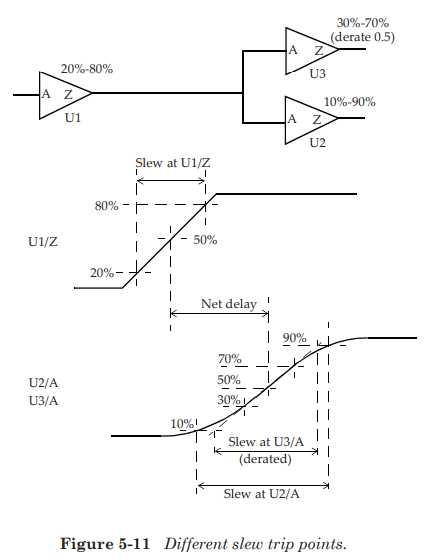

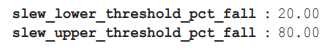

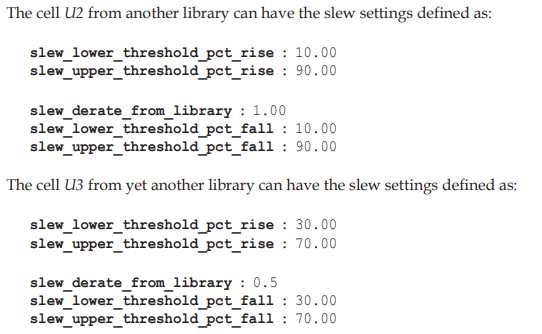

5.5不同的slew阈值

通常情况下,工艺库中会在单元特征中指定slew阈值,问题是,如果相连的两个单元slew阈值不一样,会发生什么?考虑5-11中的情景,

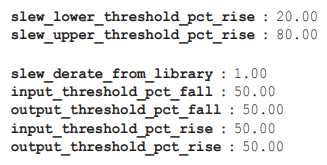

工艺库中的参数是这样的:

U1:

延时计算工具根据u2 u3输入引脚处的波形和slew阈值来计算u2 u3处输入引脚的slew(???)

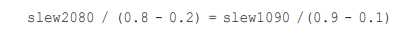

slew阈值关系:(???)

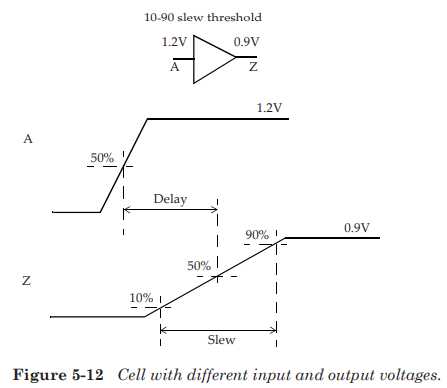

5.6不同的电压域

一个典型的设计可能会为芯片上不同的区域使用不同的电压级别。在这样的情形下,在不同的电压域借口要使用level转化单元,举例子:

5.7路径延时计算

时间通过组合逻辑单元可表现为从输入到输出的时序弧。

同样,时间通过互联线可表现为从源点到每个目标点的时序弧。

一旦整个设计被相应的时序弧标注,计算路径延时 就是 将沿着时序弧的所有连线和单元的时序弧相加。

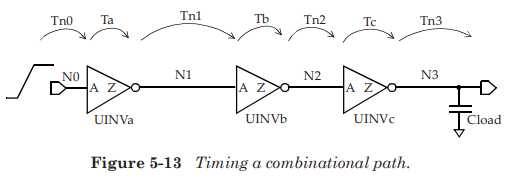

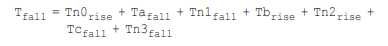

5.7.1组合逻辑路径延时

考虑3个级联反相器,上升沿和下降沿路径都考虑,现在假设在N0有上升沿。

第一个反相器的输入transition time是被指定的,未指定情况下默认为0,即理想情况。

用互联线模型来确定第一个反相器输入transition time和连线N0上的延时Tn0。

第一个反相器的输出有效电容是基于输出的RC负载获得的。

transiton time 和 有效电容 用来获得单元输出下降延时。

第一个反相器单元输出的等效戴维宁电源模型+互联线模型用于确定第二个反相器的输入transition time。

互联线模型还被用于确定延时Tn1。

Tb:输入

用UINVb/z的RC互联和UINVc的输入引脚电容决定了N2的负载。

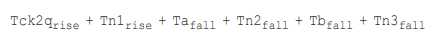

对于上面的电路,有两条时序路径,分别对应着输入上升波形和输入下降波形:

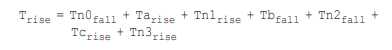

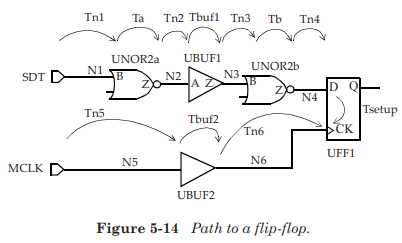

5.7.2 到触发器的路径

1.考虑下面的路径,从SDT到UFF1。

0-1路径延时:

1-0沿路径延时:

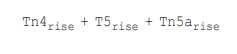

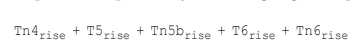

捕获路径延时:

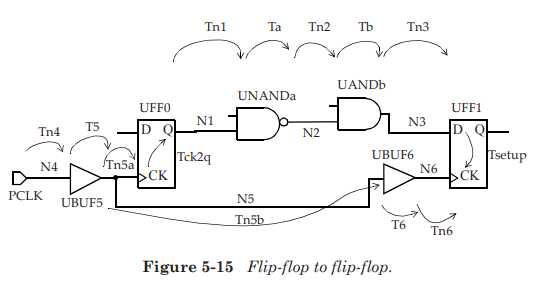

2.从寄存器到寄存器

数据路径0-1的延时:1与任何数的与非值是0 所以计算Ta 要算1-0的延时 Tn2是连线延时

发射路径的时钟延时,上升沿有效 所以考虑0-1:

捕获路径的时钟延时:

5.7.3 多路径

两个触发器之间存在最长路径和最短路径

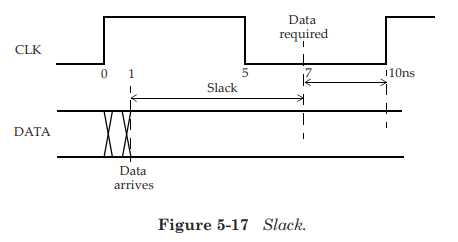

5.8 裕量计算

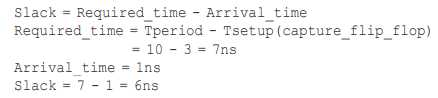

“Slack is the difference between the required time and the time that a signal arrives.”

require time从捕获触发器获得。

考虑skew 时钟偏斜

戛然而止?????

标签:diff 假设 code 多路径 就是 不同的 enc 芯片 获得

原文地址:https://www.cnblogs.com/zhanghaha-zzz/p/12899907.html