标签:entity 测试 输入 stat height 基本语法 sim str 没有

《FPGA原理与设计》课程实验教学大纲

一、实验的目的与任务:

FPGA原理与设计是电子信息类和电气类专业本科生的一门学科选修课程,FPGA原理与设计实验是学习本课程的一个重要环节。通过本课程的教学,使学生了解VHDL语言的特点,掌握Quartus II的使用方法,掌握VHDL基本语法及常用的逻辑电路,进一步加深对VHDL语言的理解,培养学生理论联系实际,提高学生分析问题、解决问题和进行科学实验的独立工作能力。

二、教学基本要求:

熟悉Quartus II软件环境和HH-SOC-EP3C40EDA/SOPC实验开发平台的使用方法;理解3-8译码器的原理和实现;理解格雷码的译码方法;掌握加法计数器的设计;掌握数码管动态显示的方法;掌握基于状态机的计数器的VHDL描述方法。

三、实验项目与类型

四、实验教学内容及学时分配:

实验一 简单的QUARTUSII实例设计

一、 实验目的

1、 通过一个简单的3—8译码器的设计,掌握组合逻辑电路的设计方法。

2、 初步了解QUARTUSII原理图输入设计的全过程。

3、 掌握组合逻辑电路的静态测试方法。

二、 实验原理

3-8译码器三输入,八输出。当输入信号按二进制方式的表示值为N时,输出端标号为N的输出端输出高电平表示有信号产生,而其它则为低电平表示无信号产生。因为三个输入端能产生的组合状态有八种,所以输出端在每种组合中仅有一位为高电平的情况下,能表示所有的输入组合。其真值表如表1-1所示:

|

输入 |

输出 |

|||||||||

|

A |

B |

C |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

|

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

|

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

|

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

|

1 |

1 |

|

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

表1-1 三-八译码器真值表

译码器不需要像编码器那样用一个输出端指示输出是否有效。但可以在输入中加入一个输出使能端,用来指示是否将当前的输入进行有效的译码,当使能端指示输入信号无效或不用对当前信号进行译码时,输出端全为高电平,表示无任何信号。本例设计中没有考虑使能输入端,自己设计时可以考虑加入使能输入端时,程序如何设计。

三、 实验内容

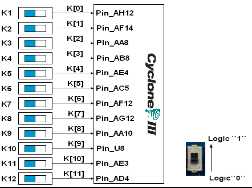

在本实验中,用三个拨动开关来表示三八译码器的三个输入(A、B、C);用八个LED来表示三八译码器的八个输出(D0-D7)。通过输入不同的值来观察输入的结果与三八译码器的真值表(表1-1)是否一致。实验箱中的拨动开关与FPGA的接口电路如下图1-1所示,当开关闭合(拨动开关的档位在下方)时其输出为低电平,反之输出高电平。

图1-1 拨动开关与FPGA接口电路

LED灯与FPGA的接口电路如图1-2所示,当FPGA与其对应的端口为高电平时LED就会发光,反之LED灯灭。

library IEEE; use IEEE.STD_LOGIC_1164.all; entity Sim381 is port(A,B,C:in STD_LOGIC; Y:out STD_LOGIC_vector(7 downto 0)); end entity Sim381; architecture tmp of Sim381 is signal s:STD_LOGIC_vector(2 downto 0); begin s <= A & B & C ; with s select Y <= "00000001" when "000", "00000010" when "001", "00000100" when "010", "00001000" when "011", "00010000" when "100", "00100000" when "101", "01000000" when "110", "10000000" when "111", "00000000" when others; end architecture tmp;

实验二 基于VHDL格雷码编码器设计

一、 实验目的

1、 了解格雷码变换的原理。

2、 进一步熟悉QUARTUSII软件的使用方法和VHDL输入的全过程。

3、 进一步掌握实验系统的使用。

二、 实验原理

格雷(Gray)码是一种可靠性编码,在数字系统中有着广泛的应用。其特点是任意两个相邻的代码中仅有一位二进制数不同,因而在数码的递增和递减运算过程中不易出现差错。但是格雷码是一种无权码,要想正确而简单的和二进制码进行转换,必须找出其规律。

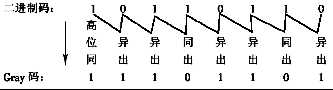

根据组合逻辑电路的分析方法,先列出其真值表再通过卡诺图化简,可以很快的找出格雷码与二进制码之间的逻辑关系。其转换规律为:高位同,从高到低看异同,异出‘1’,同出‘0’。也就是将二进制码转换成格雷码时,高位是完全相同的,下一位格雷码是‘1’还是‘0’,完全是相邻两位二进制码的“异”还是“同”来决定。下面举一个简单的例子加以说明。

假如要把二进制码10110110转换成格雷码,则可以通过下面的方法来完成,方法如图2-1。

图2-1 格雷码变换示意图

因此,变换出来的格雷码为11101101。

三、 实验内容

本实验要求完成的任务是变换12位二进制码到12位的格雷码。实验中用12位拨动开关模块的K1~K12表示8位二进制输入,用LED模块的LED1~LED12来表示转换的实验结果十二位格雷码。实验LED亮表示对应的位为‘1’,LED灭表示对应的位为‘0’。通过输入不同的值来观察输入的结果与实验原理中的转换规则是否一致。

library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_arith.all; use ieee.std_logic_unsigned.all; entity GrayCode is port(inPort:in std_logic_vector(7 downto 0); outPort:out std_logic_vector(7 downto 0) ); end GrayCode; architecture dataFlow of GrayCode is begin outPort(7) <= inPort(7); u1:for i in 0 to 6 generate outPort(i) <= (inPort(i) xor inPort(i+1)); end generate u1; end dataFlow;

实验三 加法计数器设计

一、 实验目的

1、 了解二进制计数器的工作原理。

2、 进一步熟悉QUARTUSII软件的使用方法和VHDL输入。

3、 时钟在编程过程中的作用。

二、 实验原理

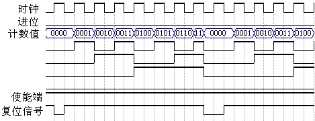

二进制计数器中应用最多、功能最全的计数器之一,含异步清零和同步使能的加法计数器的具体工作过程如下:

在时钟上升沿的情况下,检测使能端是否允许计数,如果允许计数(定义使能端高电平有效)则开始计数,否则一直检测使能端信号。在计数过程中再检测复位信号是否有效(低电平有效),当复位信号起作用时,使计数值清零,继续进行检测和计数。其工作时序如图3-1所示:

图3-1 计数器的工作时序

三、 实验内容

本实验要求完成的任务是在时钟信号的作用下,通过使能端和复位信号来完成加法计数器的计数。实验中时钟信号使用数字时钟源模块的1HZ信号,用一位拨动开关K1表示使能端信号,用复位开关S1表示复位信号,用LED模块的LED1~LED11来表示计数的二进制结果。实验LED亮表示对应的位为‘1’,LED灭表示对应的位为‘0’。通过输入不同的值模拟计数器的工作时序,观察计数的结果。实验箱中的拨动开关、与FPGA的接口电路,LED灯与FPGA的接口电路以及拨动开关、LED与FPGA的管脚连接在实验一中都做了详细说明,这里不在赘述。

数字时钟信号模块的电路原理如图3-2所示。

library ieee; use ieee.std_logic_1164.all ; use ieee.std_logic_arith.all ; use ieee.std_logic_unsigned.all ; entity Cnt_11 is port( clk , reset , En : IN std_logic ; CQ : OUT std_logic_vector( 10 downto 0 ) ); end Cnt_11 ; architecture Behaving of Cnt_11 is Begin Process ( clk , reset , En ) variable tmp : std_logic_vector( 10 downto 0 ) ; Begin if reset = ‘1‘ then --异步复位 tmp := ( others => ‘0‘ ) ; elsif Rising_Edge( clk ) then --上升沿 if En = ‘1‘ then --En始能端为1 if tmp < 10 then --在0~9时能+1 tmp := tmp + 1 ; else --否则清空 tmp := ( others => ‘0‘ ) ; end if ; end if ; end if ; --赋值给CQ CQ <= tmp ; End Process ; End Behaving ;

实验四 数码管动态显示电路的设计

一、 实验目的

1、 了解数码管的工作原理。

2、 学习七段数码管显示译码器的设计。

3、 学习VHDL的CASE语句及多层次设计方法。

二、 实验原理

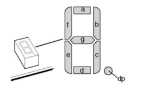

七段数码管是电子开发过程中常用的输出显示设备。在实验系统中使用的是两个四位一体、共阴极型七段数码管。其单个静态数码管如下图4-1所示。

图4-1 静态七段数码管

由于七段数码管公共端连接到GND(共阴极型),当数码管的中的那一个段被输入高电平,则相应的这一段被点亮。反之则不亮。四位一体的七段数码管在单个静态数码管的基础上加入了用于选择哪一位数码管的位选信号端口。八个数码管的a、b、c、d、e、f、g、h、dp都连在了一起,8个数码管分别由各自的位选信号来控制,被选通的数码管显示数据,其余关闭。

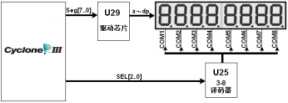

三、 实验内容

本实验要求完成的任务是在时钟信号的作用下,通过输入的键值在数码管上显示相应的键值。在实验中时,数字时钟选择1KHZ作为扫描时钟,用四个拨动开关做为输入,当四个拨动开关置为一个二进制数时,在数码管上显示其十六进制的值。实验箱中的拨动开关与FPGA的接口电路,以及拨动开关FPGA的管脚连接在实验一中都做了详细说明,这里不在赘述。数码管显示模块的电路原理如图4-2所示。

图4-2 数字时钟信号模块电路原理

library IEEE; use IEEE.std_logic_1164.all; use IEEE.std_logic_arith.all; use IEEE.std_logic_unsigned.all; entity Digit_Show is port( clk : in std_logic; Input : in std_logic_vector(3 downto 0); Digit : out std_logic_vector(7 downto 0) ); end Digit_Show; architecture Behaving of Digit_Show is begin --0x3f,0x06,0x5b,0x4f,0x66,0x6d,0x7d,0x07,0x7f,0x6f,0x77,0x7c,0x39,0x5e,0x79,0x71; -- 0 , 1 , 2 , 3 , 4 , 5 , 6 , 7 , 8 , 9 , A , B , C , D , E , F ; process(Input,clk) begin if Rising_Edge(clk) then case Input is when "0000" => Digit <="00111111"; -- 0x3f ‘0‘ when "0001" => Digit <="00000110"; -- 0x06 ‘1‘ when "0010" => Digit <="01011011"; -- 0x5B ‘2‘ when "0011" => Digit <="01001111"; -- 0x4F ‘3‘ when "0100" => Digit <="01100110"; -- 0x66 ‘4‘ when "0101" => Digit <="01101101"; -- 0x6D ‘5‘ when "0110" => Digit <="01111101"; -- 0x7D ‘6‘ when "0111" => Digit <="00000111"; -- 0x07 ‘7‘ when "1000" => Digit <="01111111"; -- 0x7F ‘8‘ when "1001" => Digit <="01101111"; -- 0x6F ‘9‘ when "1010" => Digit <="01110111"; -- 0x77 ‘A‘ when "1011" => Digit <="01111100"; -- 0x7C ‘B‘ when "1100" => Digit <="00111001"; -- 0x39 ‘C‘ when "1101" => Digit <="01011110"; -- 0x5E ‘D‘ when "1110" => Digit <="01111001"; -- 0x79 ‘E‘ when "1111" => Digit <="01110001"; -- 0x71 ‘F‘ when others => null; end case; end if ; end process; end Behaving;

实验五 基于FSM的计数器设计

一、 实验目的

1、 熟悉VHDL的FSM编程。

2、 熟悉FSM的工作原理。

3、 进一步了解实验系统的硬件结构。

二、 实验原理

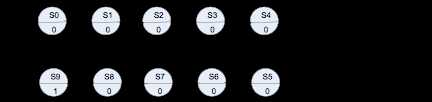

根据FSM原理,设计十进制计数器状态机,然后根据三进程方法编程。

FSM原理图如图5-1所示。

图5-1 实验原理图

Moore状态机编程结构图如图5-2所示。

图5-2 Moore状态机结构

三、 实验内容

本实验要求完成的任务是在时钟信号的作用下,通过使能端和复位信号来完成加法计数器的计数。实验中时钟信号使用数字时钟源模块的1HZ信号,用一位拨动开关K1表示使能端信号,用复位开关S1表示复位信号,用LED模块的LED1~LED11来表示计数的二进制结果。实验LED亮表示对应的位为‘1’,LED灭表示对应的位为‘0’。通过输入不同的值模拟计数器的工作时序,观察计数的结果。实验箱中的拨动开关、与FPGA的接口电路,LED灯与FPGA的接口电路以及拨动开关、LED与FPGA的管脚连接在实验一中都做了详细说明,这里不在赘述。

library ieee; use ieee.std_logic_1164.all ; entity FSM_Cnt is port( clk , inp , reset : in std_logic; outp : out std_logic_vector( 9 downto 0 ) ); end entity ; architecture behave of FSM_Cnt is type state is( s0 , s1 , s2 , s3 , s4 , s5 ,s6 , s7 , s8 , s9 ) ; signal cur_s , next_s : state ; begin main_process : process ( clk , reset ) begin if reset = ‘1‘ then cur_s <= s0 ; elsif clk‘event and clk = ‘1‘ then cur_s <= next_s ; end if; end process ; state_trans : process ( cur_s , inp ) begin case cur_s is when s0 => if inp = ‘0‘ then next_s <= s1 ;end if; when s1 => if inp = ‘0‘ then next_s <= s2 ;end if; when s2 => if inp = ‘0‘ then next_s <= s3 ;end if; when s3 => if inp = ‘0‘ then next_s <= s4 ;end if; when s4 => if inp = ‘0‘ then next_s <= s5 ;end if; when s5 => if inp = ‘0‘ then next_s <= s6 ;end if; when s6 => if inp = ‘0‘ then next_s <= s7 ;end if; when s7 => if inp = ‘0‘ then next_s <= s8 ;end if; when s8 => if inp = ‘0‘ then next_s <= s9 ;end if; when s9 => if inp = ‘1‘ then next_s <= s0 ;end if; when others => next_s <= s0 ; end case ; end process ; output_process : process ( cur_s ) begin case cur_s is when s0 => outp <= "0000000001" ; when s1 => outp <= "0000000010" ; when s2 => outp <= "0000000100" ; when s3 => outp <= "0000001000" ; when s4 => outp <= "0000010000" ; when s5 => outp <= "0000100000" ; when s6 => outp <= "0001000000" ; when s7 => outp <= "0010000000" ; when s8 => outp <= "0100000000" ; when s9 => outp <= "1000000000" ; end case ; end process ; end behave ;

标签:entity 测试 输入 stat height 基本语法 sim str 没有

原文地址:https://www.cnblogs.com/Osea/p/13192452.html