标签:输出 mic 电子 就会 图片 mem 能力 adr 实现

SDRAM(Synchronous Dynamic Random Access Memory)即同步动态随机存储器,其中的同步是指时钟信号频率与CPU保持同步,由于在进行SDRAM操作时要不断进行刷新以保证数据不会丢失,所以又叫做动态存储器。

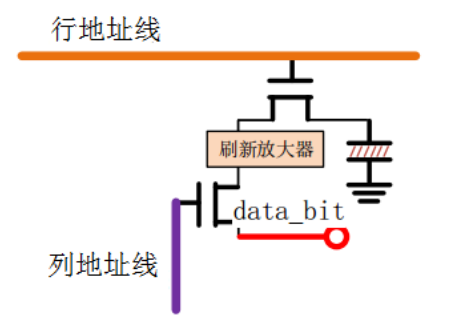

SDRAM内部存储电路原理是利用了电容能够保持电荷的能力和充放电特性,一位数据存储单元由行列选通三极管、存储电容和刷新放大器组成,在实际操作时需要选定一个行列地址,将数据线上的电平值送到电容中存储实现写操作,或者将电容状态输出到数据线上实现读操作,具体电路如图一所示:

图一 SDRAM内部存储单元电路

将如上图所示的电路作为一位数据存储单元,将其扩展为阵列,类似矩阵或者excel表格有一定的行列地址。像这样的存储表格叫做一个逻辑BANK,SDRAM规范中最高L-Bank为四个,RDRAM最多可达32个最新DDR-Ⅱ标准提高到8个。我们在表示SDRAM的基本信息时,一个存储单元并不是存储一个bit,一般是8bit的整数倍,这个存储单元的容量就是芯片的位宽,也是L-Bank的位宽,一次传输率的数据量就是芯片的位宽。

在实际操作时,我们通过具体的行列地址进行存储单元的定位,行列地址并不是同时给出的,是在选通行地址之后再给出列地址。而且选通完行地址之后,不能立马选择列地址,中间会有一个时间间隔,我们把这段时间间隔叫做tRCD(ACTIVE-to-READ or WRITE delay),tRCD是ADRAM芯片中的重要参数,不同型号和不同速度等级的芯片会有不同的tRCD值。另一种说法,由于芯片存储阵列电子元件响应时间(从一个状态到另一种状态变化的过程)而造成的一个固定延迟我们称为tRCD,即RAS到CAS延迟。

列地址有效之后,就确定了具体的存储单元,剩下的事情就是数据通过数据I/O通道(DQ)输出到内存总线。在CAS发出之后,仍要经过一定的时间才能有数据输出,从CAS与读取命令发出到第一笔数据输出的这段时间,被定义为CL(CAS Latency , CAS潜伏期)。由于CL只在读取时出现,所以CL又被称为读取潜伏期(RL , Read Latency)。

突发(burst)

突发是指在同一行中相邻的存储单元连续进行数据传输的方式,连续传输的周期数就是突发长度(Burst Lenghts,简称BL)。在进行突发传输时,只要指定起始列地址与突发长度,内存就会依次地自动对后面相应数量的存储单位进行读/写操作而不需要控制器连续地提供列地址,这样,除了第一笔数据的传输需要若干周期之外(tRCD + CL)其后面每个数据只需一个周期即可获得。

突发连续读取模式:只要指定起始列地址与突发长度,后续寻址与数据的读取自动进行,而只要控制好两端突发读取命令的间隔周期(与BL相同)即可做到连续地突发传输。

标签:输出 mic 电子 就会 图片 mem 能力 adr 实现

原文地址:https://www.cnblogs.com/16hF81F/p/14193086.html