标签:physical util rgb down sage loaded response rmi ssi

1.1 if A=4’b0011,B=3’b110 and C=4’b1110,then which one is the correct result for expression of {2{~A}}(B[1:0]&C[3:2]) ?

A. 00

~^A = ~(0&0&1&1) = ~0 = 1; {2{~^A}} = {2{1}} = 2’b11; (B[1:0]&C[3:2]) = 2’b10 & 2’b11 = 2’b10; {2{~A}}(B[1:0]&C[3:2]) = 2’b11 ^ 2’b10 = 2’b01.

1.2 Which statement is correct?

A. UVM test termination is using raise/drop uvm_object.

B. When we set the verbosity to UVM_LOW,the message with UVM_NONE cannot be issued.

C. If we set the configuration object in test layer,both subcomponents and sequences can retrieve its handle.

D. In SV language,It fails to cast a null pointer to an object. “$(abc,null);”

1.7 Please select the 4-state unsigned integer types()

A. bit. B. logic. C. reg. D. shortint.

1.8 Choose the right descriptions of the different between latch and flip-flop listed below()

A. Flip-Flop saves area. B. Latch can’t avoid glitch(毛刺). C. Flip-Flop is easier for timing closure(时序收敛). D. Latch run slower than Flip-Flop.

Latch可以组成Flip-Flop; Latch也可以避免毛刺,比如门控时钟。

1.9 Which of the following items can help reduce test time()

A. Increase Operation Voltage.

B. Increase scan shift clock frequency.

C. Utilize more scan IOs.

D. Insert gating logic.

1.11 Coverage is usually used to evaluate the verification quality, please identify all code coverage related items from following options.

A. Branch coverage.

B. Condition coverage.

C. Function coverage.

D. Toggle coverage.

E. State coverage.

F. Expression coverage.

G. FSM coverage.

1.13 Which is the correct flow for Physical Design ?

A. Floorplan → Placement → CTS → Routing

B. CTS → Floorplan → Placement → Routing

C. Placement → Floorplan → CTS → Routing

D. CTS → Placement → Floorplan → Routing

The main steps in ASIC Physical design flow are:

Design Netlist (after Synthesis);网表

Floorplanning;

Partitioning;

Placement;

Clock-Tree Synthesis (CTS);

Routing;

Physical Verification;

GDS Ⅱ Generation。

1.14 “PVT corner” is a significant concept in physical design to characterize different working conditions of a chip -P stands for Process and V stands for voltage. What does T stand for ?

A. Time. B. Temperature. C. Thickness. D. Threshold.

1.15 Which of the following metal layer has Maximum resistance?

A. Metal2. B. Metal3. C. Metal5. D. Metal8.

1.16 which of the following files are necessary for timing analysis?

A. SPEF. B. DEF. C. SDC. D. Netlist.

STA tool:

Netlist;

Library;

SDC;

Parasitic.

1.17 Which among the following methods are applicable to fix setup violation?

A. Swap high Vt cells into low Vt cells.

B. Increase driver size of long net.

C. Delaying the clock to the end point.

D. Decreasing the size of certain cells in the data path.

降低cell电压; 增加驱动; 延时时钟; 减小cell面积。

1.18 Which of the following timing arcs should a normal DFF have in stand cell library?

A. CK → D. B. CK → Q. C. D → Q. D. CK → CDN.

1.19 Cell Delay can be calculated based on:()

A. input transition. B. input load. C. output transition. D. output load.

input transition:输入数据的变换时间; output transition: 上一级数据的变换时间; input load:输入负载,负载越大input transition越小; output load:输出负载。

1.21 7nm工艺中的7nm指的是()

A. 芯片中最小晶体管的源极长度.

B. 芯片中最小晶体管的源极宽度.

C. 芯片中最小单元的沟道长度.

D. 芯片中最小单元的源极宽度.

1.22 What is the layer that TCP worked on?

A. Network. B. Data Link. C. Transport. D. Application. E. Session.

OSI七层模型:

应用层;

表示层;

会话层;

传输层;

网络层;

数据链路层;

物理层。

1.23 有一个4位的D/A转换器,设他的满刻度输出电压位10V,当输入数字量为1101时,输出电压为()

A. 8.125V. B. 4V. C. 6.25V. D. 9.375V.

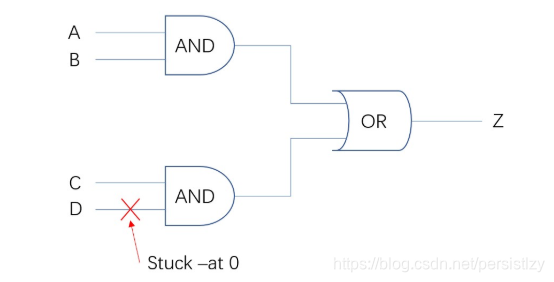

1.24 Which of below pattern can detect the fault in below diagram?

A. A=1,B=1,C=0,D=0.

B. A=1,B=1,C=1,D=1.

C. A=0,B=0,C=1,D=1.

D. A=0,B=1,C=0,D=1.

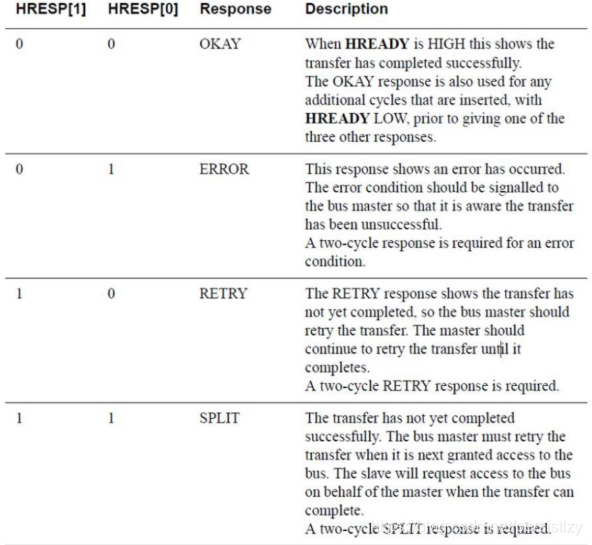

1.25 In ARM AMBA AHB protocol,which of following responses is ONE cycle response?

A. OKAY. B. ERROR. C. RETRY. D. SPLIT.

1.26 Assume A[3:0]=4’b0101,B[3:0]=4’b1111,which statement is correct()?

A. if C=&(A|B),then C=1’b0.

B. if C=(|A)&(|B),then C=1’b1.

C. if C=|(A&B),then C=1’b0.

D. if C=(&A)|(&B),then C=1’b0.

1.27 For a truth table like below,which kind of logic cell could it be?

| INPUT A | INPUT B | OUTPUT Z |

|---|---|---|

| 1 | 1 | 0 |

| 1 | 0 | 1 |

| 0 | 1 | 1 |

| 0 | 0 | 1 |

A. OR. B. NAND. C. XOR. D. NOR.

1.28 Choose the correct equation for power calculation()

A. Ptotal=Pstatic+Pdynamic.

B. Ptotal=Pleakage+Pinternal+Pswitching.

C. Ptotal=Pinternal+Pdynamic.

D. Ptotal=Pleakage+Pswitching.

1.29 We need to define clock specifications in SDC file,using commands like below:create_clock -name GFXCLK -period 600 -waveform {0 300}.What can we know from this command?

A. Clock frequency. B. Clock duty cycle. C. Clock source latency. D. Clock name.

1.30 Which is the correct method to fix EM issue?

A. downsize victim driver.

B. double net width,double net spacing,chanfe route layer.

C. insert buffer in victim net.

D. add shield.

1.31 高频放大器工作频率越高,以下说法正确的是()

A. 增益和带宽都大.

B. 增益和带宽都小.

C. 增益变大,带宽变小.

D. 增益变小,带宽变大.

1.32 PCIE

1.33 Ubuntu的内核有哪几个子系统()

A. 进程管理系统.

B. 用户管理系统.

C. I/O管理系统.

D. 文件管理系统.

E. 内存管理系统.

F. 安全管理系统.

标签:physical util rgb down sage loaded response rmi ssi

原文地址:https://www.cnblogs.com/yiquwange/p/14712995.html