标签:

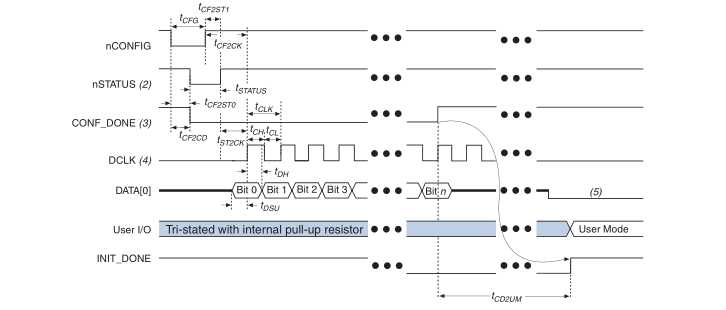

fpga 配置时序图如下

1.FPGA器件有三类配置下载方式:主动配置方式(AS)和被动配置方式(PS)和最常用的(JTAG)配置方式。

AS 由FPGA器件引导配置操作过程,它控制着外部存储器和初始化过程,EPCS系列.如EPCS1,EPCS4配置器件专供AS模式,目前只支持 Stratix II 和Cyclone系列。使用Altera串行配置器件来完成。Cyclone器件处于主动地位,配置器件处于从属地位。配置数据通过DATA0引脚送入 FPGA。配置数据被同步在DCLK输入上,1个时钟周期传送1位数据。

PS(被动串行)则由外部计算机或控制器控制配置过程。所有altera FPGA都支持这种配置模式。通过altera 的下载电缆、加强型配置器件(EPC16,EPC8,EPC4)等配置器件或智能主机(如微处理器和CPLD)来完成,在PS配置期间,配置数据从外部储存部件(这些存储器可以是altera配置器件或单板上的其他flash器件),通过DATA0引脚送入FPGA。配置数据在DCLK上升沿锁存,1个时钟周期传送1位数据。FPP(快速被动并行):该配置模式只有在stratix系列和APEX II中支持;PPA(被动并行异步):该配置模式在stratix 系列、APEX II、APEX 20K、mercury、ACEX 1K和FLEX 10K中支持;PPS(被动并行同步):这种模式只有一些较老的器件支持,APEX II、APEX 20K、mercury、ACEX 1K和FLEX 10K。PSA(被动串行异步):只有在FLEX 6000器件中支持。

JTAG接口是一个业界标准,主要用于芯片测试等功能,使用IEEE Std 1149.1联合边界扫描接口引脚,支持JAM STAPL标准,可以使用Altera下载电缆或主控器来完成。

FPGA配置过程:

在FPGA正常工作时,配置数据存储在SRAM中,这个SRAM单元也被称为配置存储器(configure RAM)。由于SRAM是易失性存储器,因此在FPGA上电之后,外部电路需要将配置数据重新载入到芯片内的配置RAM中。在芯片配置完成之后,内部的寄存器以及I/O管脚必须进行初始化(initialization),等到初始化完成以后,芯片才会按照用户设计的功能正常工作,即进入用户模式。

FPGA上电以后首先进入配置模式(configuration),在最后一个配置数据载入到FPGA以后,进入初始化模式(initialization),在初始化完成后进入用户模式(user-mode)。在配置模式和初始化模式下,FPGA的用户I/O处于高阻态(或内部弱上拉状态),当进入用户模式下,用户I/O就按照用户设计的功能工作。

altera FPGA配置全过程:一个器件完整的配置过程将经历复位、配置和初始化等3个过程。FPGA正常上电后,当其nCONFIG管脚被拉低时,器件处于复位状态,这时所有的配置RAM内容被清空,并且所有I/O处于高阻态,FPGA的状态管脚nSTATUS和CONFIG_DONE管脚也将输出为低。当FPGA的nCONFIG管脚上出现一个从低到高的跳变以后,配置就开始了,同时芯片还会去采样配置模式(MSEL)管脚的信号状态,决定接受何种配置模式。随之,芯片将释放漏极开路(open-drain)输出的nSTATUS管脚,使其由片外的上拉电阻拉高,这样,就表示FPGA可以接收配置数据了。在配置之前和配置过程中,FPGA的用户I/O均处于高阻态。

在接收配置数据的过程中,配置数据由DATA管脚送入,而配置时钟信号由DCLK管脚送入,配置数据在DCLK的上升沿被锁存到FPGA中,当配置数据被全部载入到FPGA中以后,FPGA上的CONF_DONE信号就会被释放,而漏极开路输出的CONF_DONE信号同样将由外部的上拉电阻拉高。因此,CONF_DONE管脚的从低到高的跳变意味着配置的完成,初始化过程的开始,而并不是芯片开始正常工作。

INIT_DONE是初始化完成的指示信号,它是FPGA中可选的信号,需要通过Quartus II工具中的设置决定是否使用该管脚。在初始化过程中,内部逻辑、内部寄存器和I/O寄存器将被初始化,I/O驱动器将被使能。当初始化完成以后,器件上漏极开始输出的INIT_DONE管脚被释放,同时被外部的上拉电阻拉高。这时,FPGA完全进入用户模式,所有的内部逻辑以及I/O都按照用户的设计运行,这时,那些FPGA配置过程中的I/O弱上拉将不复存在。不过,还有一些器件在用户模式下I/O也有可编程的弱上拉电阻。在完成配置以后,DCLK信号和DATA管脚不应该被浮空(floating),而应该被拉成固定电平,高或低都可以。

如果需要重新配置FPGA,就需要在外部将nCONFIG重新拉低一段时间,然后再拉高。当nCONFIG被拉低吼,nSTATUS和CONF_DONE也将随即被FPGA芯片拉低,配置RAM被清,所有I/O都变成三态。当nCONFIG和nSTATUS都变为高时,重新配置就开始了。

主动串行(AS)

AS配置器件是一种非易失性、基于flash存储器的存储器,用户可以使用altera的ByteBlaster II加载电缆、altera的“altera programming unit”或者第三方的编程器来对配置芯片进行编程。它与FPGA的接口为以下简单的4个信号线:

. 串行时钟输入(DCLK):是在配置模式下FPGA内部的振荡器(oscillator)产生的,在配置完成后,该振荡器将被关掉。工作时钟在20MHz左右,而fast AS方式下(stratix II和cyclone II支持该种配置方式),DCLK时钟工作在40MHz左右,在altera的主动串行配置芯片中,只有EPCS16和EPCS64的DCLK可以支持到40MHz,EPCS1和EPCS4只能支持20MHz。

. AS控制信号输入(ASDI)

. 片选信号(nCS);

. 串行数据输出(DATA)。

多片配置:控制配置芯片的FPGA为“主”,其后面的FPGA为“从”。主片的nCE需要直接接地,其nCEO输出脚驱动从片的nCE,而从片的nCEO悬空,nCEO脚在FPGA未配置时输出为低。这样,AS配置芯片中的配置数据首先写到主片的FPGA中,当其接收到它的所有的配置数据以后,随即驱动nCEO信号为高,使能从片的FPGA,这样配置芯片后面的读出的数据将被写入到从片的FPGA中。在生成配置文件对串行配置器件编程时,Quartus II工具需要将两个配置文件合并到一个AS配置文件中,编程到配置器件中。如果这两个FPGA的配置数据完全一样,就可以将从片的nCE也直接接地,这样只需要在配置芯片中放一个配置文件,两个FPGA同时配置。

被动串行(PS):

是使用最多的一种配置方式。与FPGA的信号接口:

. DCLK(配置时钟);

. DATA0(配置数据);

. nCONFIG(配置命令);

. nSTATUS(状态信号);

.CONF_DONE(配置完成指示)。

在PS方式下,FPGA处于完全被动的地位。FPGA接收配置时钟、配置命令和配置数据,给出配置的状态信号以及配置完成指示信号等。PS配置可以使用altera的配置器件(EPC1、EPC4等),可以使用系统中的微处理器,也可以使用单板上的CPLD,或者altera的下载电缆,不管配置的数据源从哪里来,只要可以模拟出FPGA需要的配置时序来,将配置数据写入FPGA就可以。

在上电以后,FPGA会在nCONFIG管脚上检测到一个从低到高的跳变沿,因此可以自动启动配置过程。

支持多片配置方式。

JTAG配置方式:

JTAG接口是一个业界标准接口,主要用于芯片测试等功能。altera FPGA基本上都可以支持JTAG命令来配置FPGA的方式,而且JTAG配置方式比其他任何方式优先级都高。JTAG接口有4个必需的信号TDI, TDO, TMS和TCK以及1个可选信号TRST构成,其中:

. TDI,用于测试数据的输入;

. TDO,用于测试数据的输出;

. TMS,模式控制管脚,决定JTAG电路内部的TAP状态机的跳变;

. TCK,测试时钟,其他信号线都必须与之同步;

. TRST,可选,如果JTAG电路不用,可以讲其连到GND。

用户可以使用altera的下载电缆,也可以使用微处理器等智能设备从JTAG接口设置FPGA。

nCONFIG、MESL和DCLK信号都是用在其他配置方式下。如果只用JTAG配置,则需要将nCONFIG拉高,将MSEL拉成支持JTAG的任一方式,并将DCLK拉成高或低的固定电平。JTAG配置方式支持菊花链方式,级联多片FPGA。

FPGA 在正常工作时,它的配置数据存储在SRAM中,加电时须重新下载。在实验系统中,通常用计算机或控制器进行调试,因此可以使用PS。在实用系统中,多数情况下必须由FPGA主动引导配置操作过程,这时FPGA将主动从外围专用存储芯片中获得配置数据,而此芯片中fpga配置信息是用普通编程器将设计所得的 pof格式的文件烧录进去。

专用配置器件:epc型号的存储器

常用配置器件:epc2,epc1,epc4,epc8,epc1441(现在好象已经被逐步淘汰了)等。

对于cyclone cycloneII系列器件,ALTERA还提供了针对AS方式的配置器件,EPCS系列.如EPCS1,EPCS4配置器件也是串行配置的.注意,他们只适用于cyclone系列.

除 了AS和PS等单BIT配置外,现在的一些器件已经支持PPS,FPS等一些并行配置方式,提升配置了配置速度。当然所外挂的电路也和PS有一些区别。还有处理器配置比如JRUNNER 等等,如果需要再baidu吧,至少不下十种。比如Altera公司的配置方式主要有Passive Serial(PS),Active Serial(AS),Fast Passive Parallel(FPP),Passive Parallel Synchronous(PPS),Passive Parallel Asynchronous(PPA),Passive Serial Asynchronous(PSA),JTAG等七种配置方式,其中Cyclone支持的配置方式有PS,AS,JTAG三种.

2 对FPGA芯片的配置中,可以采用AS模式的方法,如果采用EPCS的芯片,通过一条下载线进行烧写的话,那么开始的"nCONFIG,nSTATUS"应该上拉,要是考虑多种配置模式,可以采用跳线设计。让配置方式在跳线中切换,上拉电阻的阻值可以采用10K

3, 在PS模式下tip:如果你用电缆线配置板上的FPGA芯片,而这个FPGA芯片已经有配置芯片在板上,那你就必须隔离缆线与配置芯片的信号。一般平时调试时不会把配置芯片焊上的,这时候用缆线下载程序.只有在调试完成以后,才把程序烧在配置芯片中, 然后将芯片焊上.或者配置芯片就是可以方便取下焊上的那种.这样出了问题还可以方便地调试.

在AS模式下tip: 用过一块板子用的AS下载,配置芯片一直是焊在板子上的,原来AS方式在用线缆对配置芯片进行下载的时候,会自动禁止对FPGA的配置,而PS方式需要电路上隔离。

4,一般是用jtag配置epc2和flex10k, 然后 epc2用ps方式配置flex10k.这样用比较好.(这是我在网上看到的,可以这样用吗?怀疑中)望达人告知.

5, 下载电缆,Altera下的下载电缆分为byteblaster和byteblasterMV,以及ByteBlaster II,现在还推出了基于USB-blaster.由于BB基本已经很少有人使用,而USB-Blaster现在又过于昂贵,这里就说一下BBII和 BBMV的区别.

BBII支持多电压供电5.5v,3.3v,2.5v,1.8v;

BBII支持三种下载模式:AS,可对Altera的As串行配置芯片(EPCS系列)进行编程

PS,可对FPGA进行配置

JTAG,可对FPGA,CPLD,即Altera配置芯片(EPC系列)编程

而BBMV只支持PS和JTAG

6, 一般在做FPGA实验板,(如cyclone系列)的时候,用AS+JTAG方式,这样可以用JTAG方式调试,而最后程序已经调试无误了后,再用AS模式把程序烧到配置芯片里去,而且这样有一个明显的优点,就是在AS模式不能下载的时候,可以利用Quartus自带的工具生成JTAG模式下可以利用的jic文件来验证配置芯片是否已经损坏,方法祥见附件(这是骏龙的人写的,摘自咱们的坛子,如有版权问题,包涵包涵).

7.Altera的FPGA可以通过单片机,CPLD等加以配置,主要原理是满足datasheet中的时序即可,这里我就不多说了,有兴趣的朋友可以看看下面几篇文章,应该就能够明白是怎么回事了.

8.配置时,quartus软件操作部分:

(1).assignment-->device-->device&pin options-->选择configuration scheme,configuaration mode,configuration device,注意在不支持远程和本地更新的机器中configuration mode不可选择,而configuration device中会根据不同的配置芯片产生pof文件,如果选择自动,会选择最小密度的器件和适合设计

(2).可以定义双口引脚在配置完毕后的作用,在刚才的device&pin option-->dual-purpose pins-->,可以在配置完毕后继续当I/O口使用

(3).在general菜单下也有很多可钩选项,默认情况下一般不做改动,具体用法参见altera configuration

handbook,volume2,sectionII.

(4)关于不同后缀名的文件的适用范围:

sof(SRAM Object File):当直接用PS模式下将配置数据下到FPGA里用到、 USB ASTER, MASTERBLASER, BBII,BBMV适用、quartusII会自动生成,所有其他的配置文件都是由sof生成的.

pof(Programmer Object File)也是由quartusII自动生成的,BBII适用,AS模式下将配置数据下到配置芯片中

rbf(Raw Binary File)用于微处理器的二进制文件.在PS,FPP,PPS,PPA配置下有用处

rpd(Raw Programing Data File)包含bitstream的二进制文件,可用AS模式配置,只能由pof文件生成

hex(hexadecimal file)这个就不多说了,单片机里很多

ttf(Tabular Text File)适用于FPP,PPS,PPA,和bit-wide PS配置方式

sbf(Serial Bitstream File)用PS模式配置Flex 10k和Flex6000的

jam(Jam File)专门用于program,verigy,blank-check

标签:

原文地址:http://www.cnblogs.com/lianjiehere/p/4274137.html