标签:

cb早在2012年就推出了VIP 视频开发板 V1.4 这套开发板是ep2的,摄像头是ov7670,虽然不如当前的vip20强大,但也算是其雏形。

在vip20后期,cb对sdram以及其他模块进行了封装,使其更可靠,更稳定。

显然,sdram要更稳定,更可靠,验证,需要进行大量的实验,使用多种ic,然而经验丰富的cb,也有遗漏的测试(ps:注意上一篇博客细节)

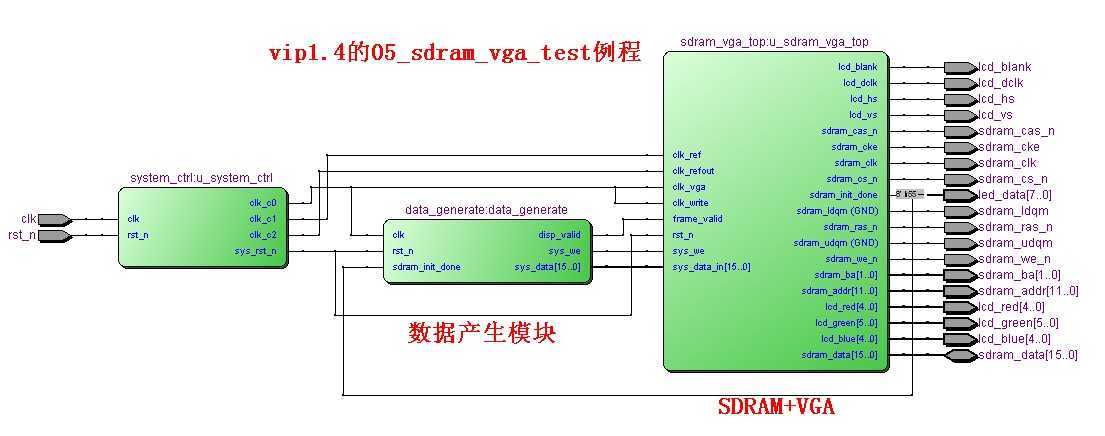

于是找到vip1.4的05_sdram_vga_test例程,果不其然,这个例程兼容性很好,vip2.0不能使用的程序使用这个是可以的。

好了,下面我需要把1.4的程序重新移植到2.0上,验证起兼容性

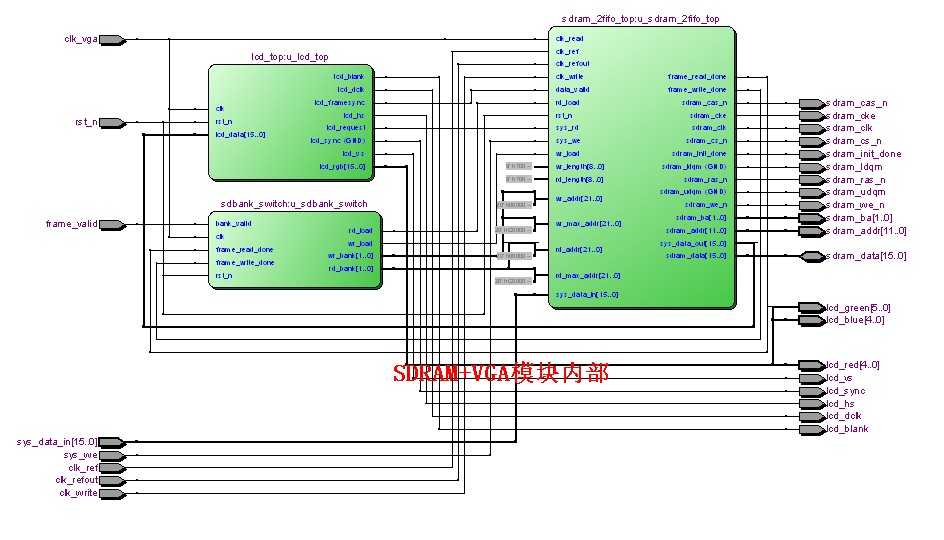

先看看接口

rtl

看完以上接口

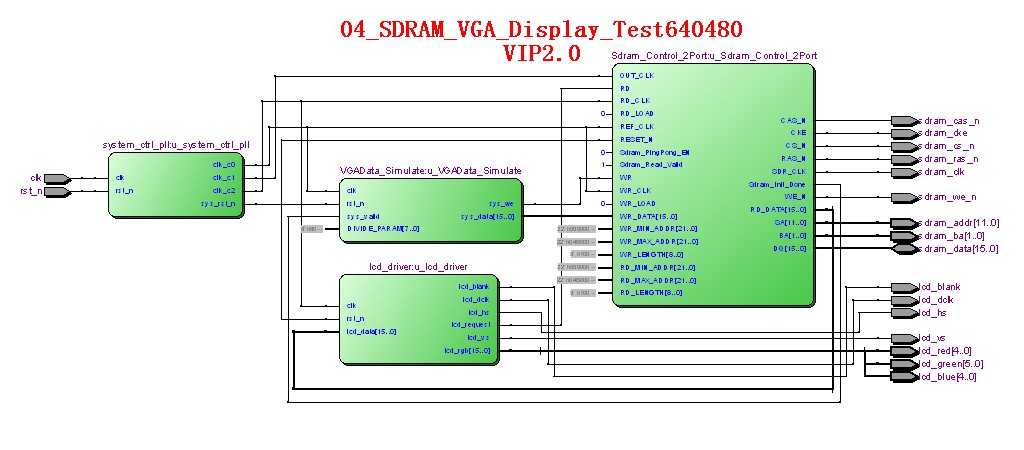

在和VIP2.0的主流结构对比下

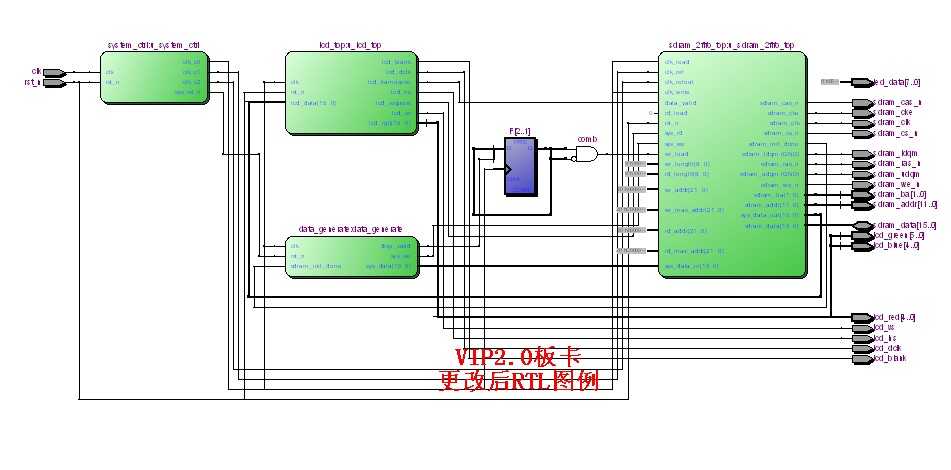

更改如下:针对 vip1.4

1、sdram_vga_top 拆分 为 vga 和 sdram 放在顶层

2、sdram_vga_top 内部 去掉 sdbank_switch 模块,因为关联太多信号,去掉此模块是为了精简,简化,暂时用不着乒乓等功能。

3、sdram接口处理

.wr_addr ({20‘d0}), //sdram start write address

.wr_max_addr ({20‘d786432}), //sdram max write address

.wr_load (WR_LOAD), //sdram write address reset

.rd_addr ({20‘d0}), //sdram start read address

.rd_max_addr ({20‘d786432}), //sdram max read address

.rd_load (0), //sdram read address reset

4、增加触发信号

reg F1;

reg F2;

reg F3;

reg F4;

reg F5;

always@(posedge clk_write)

begin

F1<=frame_valid;

F2<=F1;

F3<=F2;

F4<=F3;

F5<=F4;

end

wire WR_LOAD=pos_edge;

wire neg_edge = !F1 & F2;

wire pos_edge = F1 & !F2;

自此已经完成测试。

标签:

原文地址:http://www.cnblogs.com/ccjt/p/4425614.html