标签:

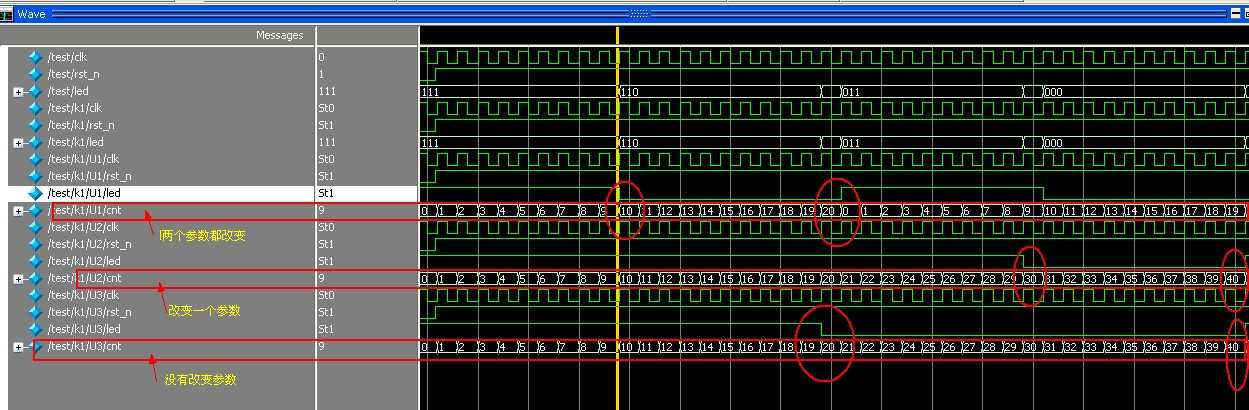

一、在引用实例时可以通过 #(A,B,C)来改变参数。如果#()内的参数个数比实例中参数个数少,则实例中后面部分参数不改变。默认按顺序对应。

例子:

module parameter_top ( clk, rst_n, led ); input clk; input rst_n; output [2:0] led; //----------------------------// test_led #(10,20) U1( .clk(clk), .rst_n(rst_n), .led(led[0]) ); test_led #(30) U2( .clk(clk), .rst_n(rst_n), .led(led[1]) ); test_led U3( .clk(clk), .rst_n(rst_n), .led(led[2]) ); endmodule module test_led ( clk, rst_n, led ); input clk; input rst_n; output led; //---------------------------// parameter tck = 20; parameter tcf = 40; reg [5:0] cnt; always @(posedge clk or negedge rst_n) begin if(!rst_n) begin cnt <= 0; end else if(cnt >= tcf ) begin cnt <= 0; end else cnt <= cnt + 1; end assign led = (cnt < tck ); endmodule

测试程序:

/********************************Copyright************************************** **----------------------------File information-------------------------- ** File name :test.v ** CreateDate :2015.06 ** Funtions :测试文件 ** Operate on :M5C06N3L114C7 ** Copyright :All rights reserved. ** Version :V1.0 **---------------------------Modify the file information---------------- ** Modified by : ** Modified data : ** Modify Content: *******************************************************************************/ module test; reg clk; reg rst_n; wire [2:0] led; parameter_top k1( .clk, .rst_n, .led ); //-------------------// parameter tck = 24; parameter t = 1000/tck; always #(t/2) clk = ~clk; initial begin clk = 0; rst_n = 0; #(15*t) rst_n = 1; end endmodule

测试波形:

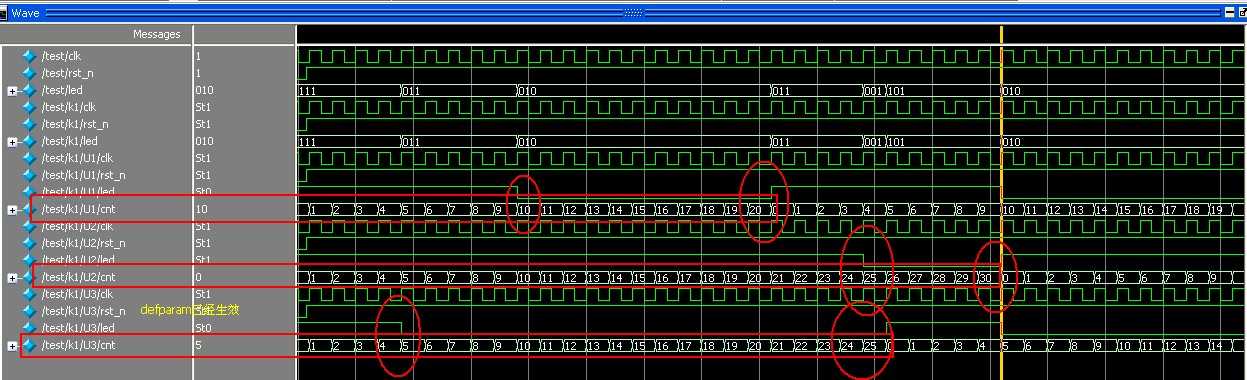

二、还可以在TOP文件中通过defparam 来改变参数,格式为 defparam 例化名.内层例化名.参数名 = 数值。例如:在top中例化,U1.S1.K = 2;

例子:

module parameter_top_2 ( clk, rst_n, led ); input clk; input rst_n; output [2:0] led; //----------------------------// test_led U1( .clk(clk), .rst_n(rst_n), .led(led[0]) ); test_led U2( .clk(clk), .rst_n(rst_n), .led(led[1]) ); test_led U3( .clk(clk), .rst_n(rst_n), .led(led[2]) ); defparam U1.tck = 10; defparam U1.tcf = 20; defparam U2.tck = 25, //,不是; U2.tcf = 30; defparam U3.tck = 5; defparam U3.tcf = 25; endmodule module test_led ( clk, rst_n, led ); input clk; input rst_n; output led; //---------------------------// parameter tck = 20; parameter tcf = 40; reg [5:0] cnt; always @(posedge clk or negedge rst_n) begin if(!rst_n) begin cnt <= 0; end else if(cnt >= tcf ) begin cnt <= 0; end else cnt <= cnt + 1; end assign led = (cnt < tck ); endmodule

测试程序:

module test; reg clk; reg rst_n; wire [2:0] led; parameter_top_2 k1( .clk, .rst_n, .led ); //-------------------// parameter tck = 24; parameter t = 1000/tck; always #(t/2) clk = ~clk; initial begin clk = 0; rst_n = 0; #(15*t) rst_n = 1; end endmodule

仿真图片:

标签:

原文地址:http://www.cnblogs.com/fhyfhy/p/4546001.html