标签:

ARM v7-A 系列CPU的MMU隐射分析

摘要:ARM v7-A系列的CPU加入了很多扩展,如多核处理器扩展、大物理地址扩展、TrustZone扩展、虚拟化扩展。若支持大的物理地址,则必须支持多核处理器;若支持虚拟化,则必须支持大的物理地址、多核处理器、TrustZone。加入这些扩展后,相应的MMU(虚拟地址到物理地址的隐射功能)结构也改变了许多。本文首先分析加入扩展后MMU的整体结构,然后详细介绍地址转换中用到短描述符格式(32位)和长描述符格式(64位),以及如何实现虚拟地址到物理地址的查询,最后就二级隐射问题,给出一个例子用以验证。

关键字:Cortex-A MMU;大物理地址扩展;TrustZone;虚拟化;二级隐射

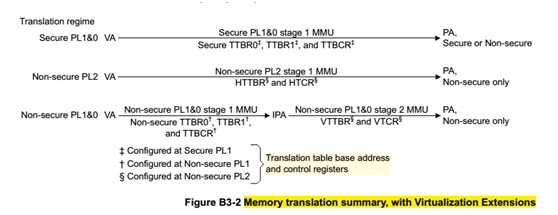

整体结构由四部分组成,如下图所示。

PL2:NS(非安全模式)下的HYP(超级管理)模式

PL1:S(安全模模式)或者NS(非安全模式)下的其它模式(用户模式除外)

PL0:S或者NS下的用户模式

注:每个CPU(支持TrustZone扩展)可以处于安全模式或者非安全模式,处于任意模式(安全或者非安全)的CPU又有8个模式(支持TrustZone、虚拟化)。

这四部分为:

安全模式的PL1&0隐射,页表控制寄存器TTBCR,页表基址寄存器TTBR0/TTBR1,这些寄存器需要在S模式的PL1设置;

非安全模式的PL2隐射,页表控制寄存器HTCR,页表基址寄存器HTTBR,需要在NS的PL2设置;

非安全模式的PL1&0的一级映射,页表控制寄存器TTBCR,页表基址寄存器TTBR0/TTBR1,需要在NS模式的PL1设置;

非安全模式的PL1&0的二级映射,页表控制寄存器VTCR,页表基址寄存器VTTBR,需要在NS的PL2设置;

由于扩展了很多,带来了下面几个问题:

1、处于安全模式的CPU,用MMU访问相应的物理单元时,同样的虚拟地址,可以访问到安全的物理地址,也可能访问到非安全的物理地址,怎么决定访问的物理地址是安全的、非安全的?

处于非安全模式的CPU是没有这个功能的,只能访问到非安全的物理地址。

答:对于采用短描述符,若一级描述符是段或者超级段,则第19位NS表示访问的是S/NS;

若一级描述符是页表,则第3位NS表示访问的是S/NS,

就是二级描述符不再区分了,即S/NS的区分是以1MB为单位的。

对于采用长描述符格式,二级映射只在NS模式下才使用,而S/NS之分只在S模式下使用,故只有一级映射才有该功能。

若一级描述符是block,则第5位NS表示访问的是S/NS,只是在查询出最终的物理地址时才有用。

若一级描述符是table,则第63位NS Table表示是S/NS,

若为1,则后续的二级、三级都是非安全的;

若为0,若二级是block,则NS决定;

若二级也是table,继续判断 NS TABLE

若为1,则后面的是非安全的。

若为0,则三级的第5位NS决定。

2、NS PL1&0 是否启用二级映射,能否不采用?

答:HCR寄存器的VM位,决定NS PL1&0的二级映射是否使能

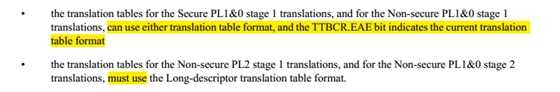

3、短/长描述符格式怎么选取,S PL1&0,NS PL1&0的一级映射怎么决定采用短描述符格式、长描述符格式?

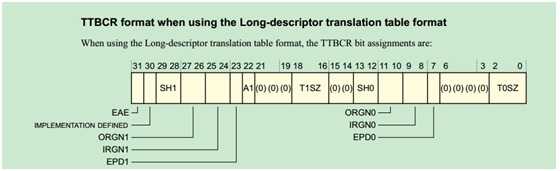

答: 参考上面的描述,TTBCR的EAE位决定采用短或者长;而NS的PL2,NS的PL1&0的二级映射必须采用长描述符格式。

输入的虚拟地址是32位,输出的物理地址是32位/40位。

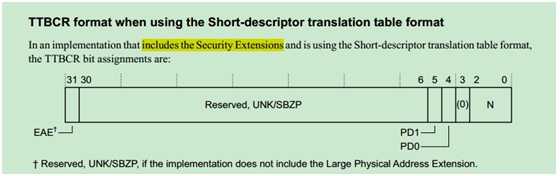

32位的TTBCR的格式:

32位的TTBR0格式:

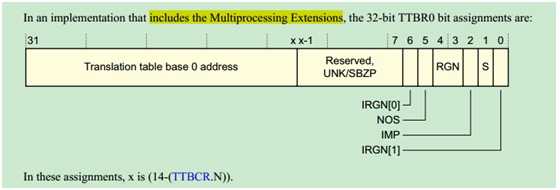

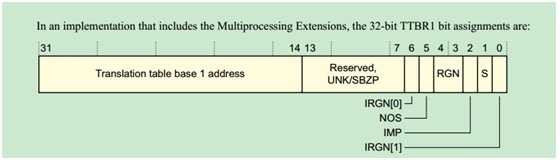

32位的TTBR1格式:

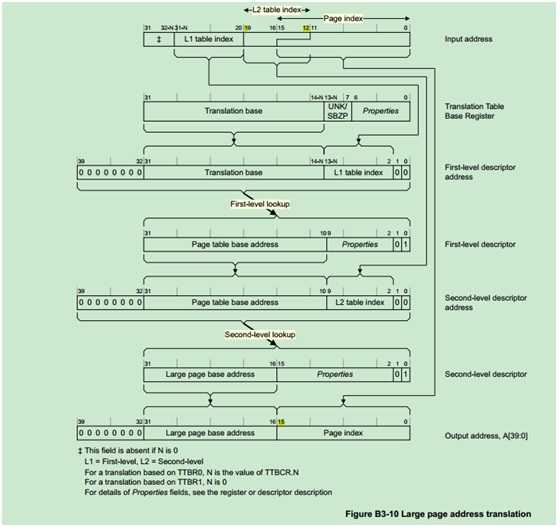

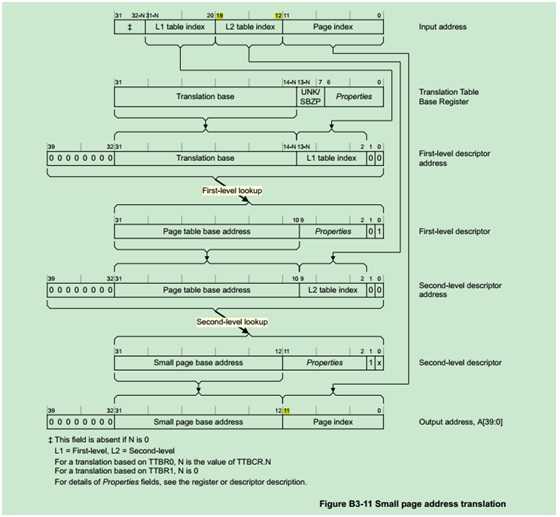

隐射分类:

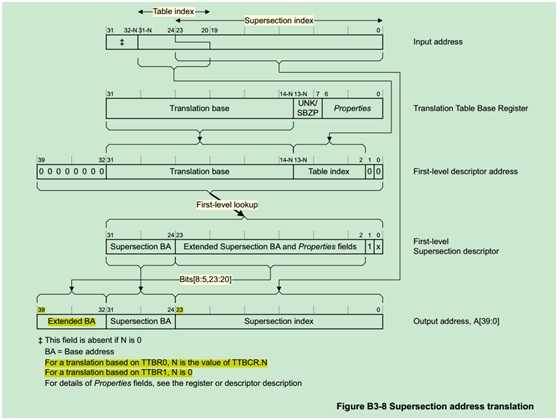

超级段:24位,16MB,是否支持,由实现决定(Cortex-A7,A9都是不同的实现)。物理地址最大可以到40位

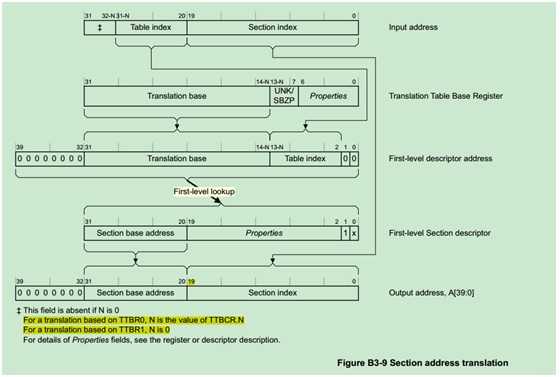

段: 20位,1MB

大页: 16位,64KB

小页: 12位,4KB

短描述符总共可能有二级,分别描述如下。

一级描述符内容:

00:无效

01:页表,[31:10] 位是二级页表的基地址

1X:段隐射,X是PXN(Privileged execute never)位。

18位是0则是段,是1则为超级段。

段,则用[31:20]表示物理地址的高12位,虚拟地址的低20位也是物理地址的;

超级段,[39:36(8:5) 35:32(23:20)31:24] 共16位,组成物理地址的高16位,虚拟地址的低24位也是物理地址的

PXN:没有实现大的物理地址扩展时,这个位是可选的(定义或不定义);

若实现了,则这个位必须定义。

二级描述符内容:

00:无效

01:大页,31:16表示物理地址的高位,虚拟地址的低16位也是物理地址的,

1X:小页,31:12表示物理地址的高位,虚拟地址的低12位也是物理地址的。

X是XN(execute never)位,能否执行位

TTBR0或者TTBR1的选取:

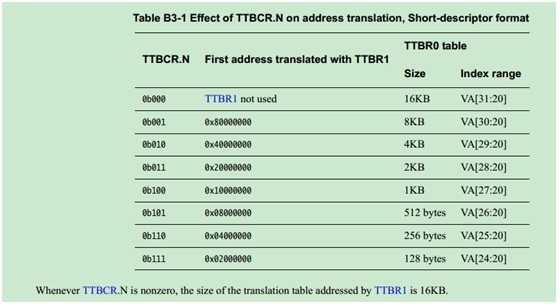

TTBCR的2:0这3位的内容,就是N。

若N是0,则一直用TTBR0;

若N>0,则按照下面表格内容推断。

N最大是7,若N是7,则0x0200 0000 ~ 0x03FF FFFF开头的虚拟地址采用TTBR0,这个总共0x20个,每个4字节,故TTBR0只需128字节就可;

而对于TTBR1,因为地址不连续,则需要16KB的大小,16KB/4=4KB,4*1024*1MB=4GB,就覆盖了整个范围。

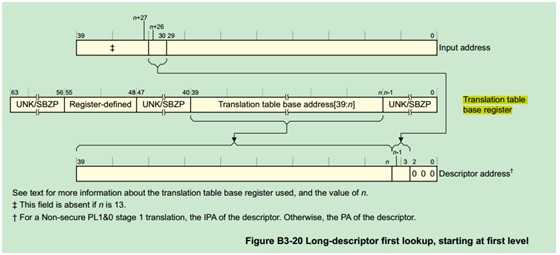

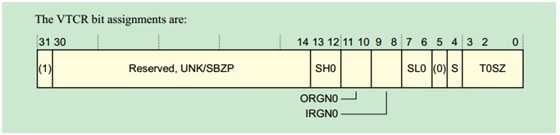

总共可能有三级,分别描述如下。

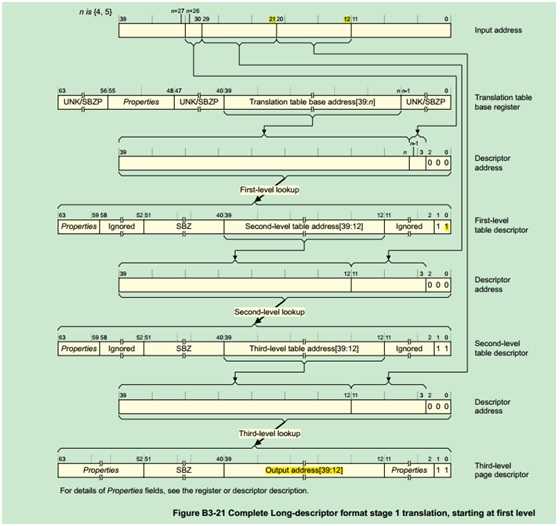

一级查询示意如下图所示。

对于stage 1隐射:输入32位,输出40位

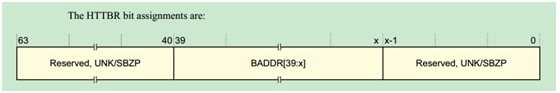

HYP模式下,64位的HTTBR定义如下。

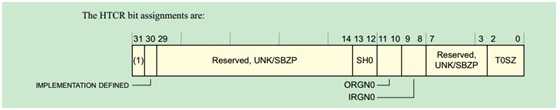

根据HTCR.T0SZ(就是HTCR低3位的值),确定X的值。

若HTCR.T0SZ > 1,则是14 - HTCR.T0SZ;否则是5 - HTCR.T0SZ。

32位的HTCR定义如下。

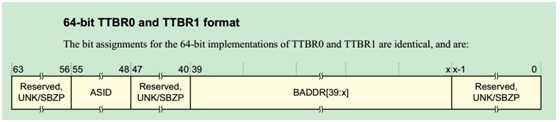

其它模式下,64位的TTBR0/TTBR1定义如下。

其中X的值,由TTBCR.T0SZ/T1SZ决定,公式同上。

TTBCR的第22位A1,决定采用TTBR0或者是TTBR1的ASID(地址空间ID)

32位的TTBCR定义如下。

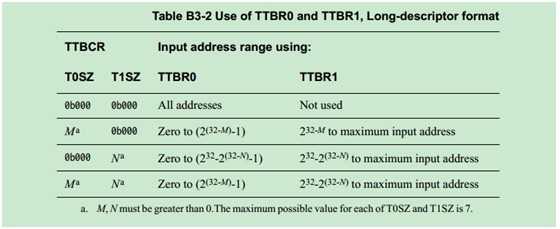

TTBR0或者TTBR1的选取:

参考下面的表格公式,可能出现某段虚拟地址空间,找不到页表基地址,无法被访问。

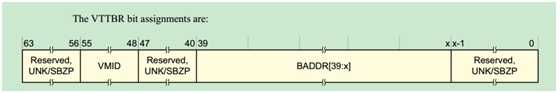

对于Stage 2隐射:输入40位,输出40位。

64位的VTTBR定义如下所示。

其中X的值,由VTCR.T0SZ决定,计算方法同上。

32位的VTCR定义如下。

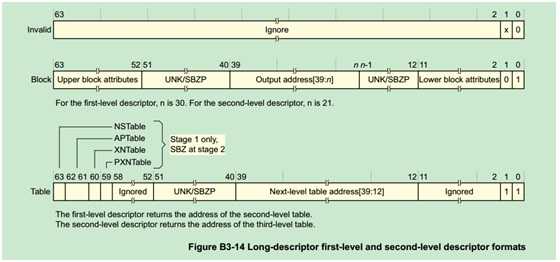

一级查询和二级查询的描述符格式如下图所示。

根据上图,若一级查询出来是block,则取出39:30作为地址的高位,虚拟地址的30:0作为低位,大小是以1GB为单元。

若一级查询出来的是页表,则根据取出的39:12作为高地址,虚拟地址的29:21充当11:3低位,继续查询。

根据上图,若查询出来的是block,则取出39:21作为物理地址的高位,虚拟的20:0作为低位,大小是以2MB为单元。

若查询出来的仍然是页表,则取出39:12作为高地址,再次将虚拟地址的20:12充当11:3位,继续查询。

一级映射下,一次完整的三级查询如下图所示。

根据上图,三级查询结果一定是页表,将取出来的39:12作为物理的高地址,虚拟地址的11:0作为低地址,这就是最终的物理地址。

验证平台:

内存大小2GB:0x0000 0000 ~ 0x8000 0000

CPU:Cortex-A7

UBOOT中设置传递给内核的内存地址大小为1024-16M,地址范围为 0x0000 0000 ~ 0x4000 0000 -16MB。

开启NS下的二级隐射功能。设置VTTBR的地址为table_base_stage_2,二级隐射的页表内容如下。

.globl table_base_stage_2

table_base_stage_2:

.quad 0x00000000000007FD // Mapping guest‘s IPA 0x0000,0000-0x3FFF,FFFF to PA 0x0000,0000-0x3FFF,FFFF (RAM space)

.quad 0x0000000000000000

.quad 0x00400000800004C9 // Mapping guest‘s IPA 0x8000,0000-0xBFFF,FFFF to PA 0x8000,0000-0xBFFF,FFFF (Device space)

.quad 0x00400000800004C9 // Mapping guest‘s IPA 0xC000,0000-0xFFFF,FFFF to PA 0xC000,0000-0xFFFF,FFFF (Device space)

.quad 0x0000000000000000 // Mark everything else as aborting

.quad 0x0000000000000000

每个描述符内容64位,8个字节。

第一个 0x0000 0000 0000 07FD,[39:30]是[0000 0000 00], 最低位是1 1 0 1,表明是个块映射。即IPA 0xXX 0000 0000 ~ 0xXX 3FFF FFFF这段地址空间对应的

物理地址是个块,对应的物理地址范围是0x00 0000 0000 ~ 0x00 3FFF FFFF。

对于第二个,0x0000000000000000,最低位是0 0 0 0,则根据下面的描述,

即IPA 0x4000 0000 ~ 0x7FFF FFFF对应的PA是不确定的,会产生转换失效。

内核中,建立一个16M的短描述符的段隐射,隐射描述为:

虚拟地址0xFD00 0000 ~ FE00 0000 对应的IPA中间地址是0x 4000 0000 ~ 0x4100 0000。

然后内核访问0xfd00 0004这个虚拟地址空间,根据一级隐射,对应的IPA是0x4000 0004;

而在二级隐射中,这个IPA地址找不到对应的物理地址,就会出错,但是不会panic,观察显示这个线程占用了90%多的CPU。

参考文献:DDI0406C_arm_architecture_reference_manual.pdf

标签:

原文地址:http://www.cnblogs.com/fozu/p/4601291.html