标签:软件 正弦 class 介绍 make atl inf 文件中 sim

在VIVADO FIR滤波器设计与仿真(一)中产生了两路正弦信号,频率分别为4MHz和5MHz,今天要进行FIR滤波器设计,在进行滤波器设计之前,需要对滤波器的参数进行设置,需要借助MATLAB软件或者Filter Solutions软件,这次使用Filter Solutions来进行参数设定。

关于Filter Solutions软件的使用,这里有一篇博客比较详细的介绍了它的用法,可以作为参考:

Filter Solutions之滤波器设计

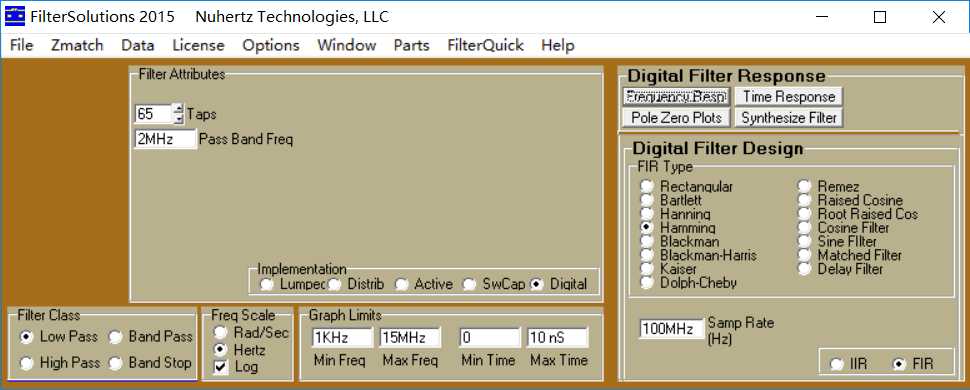

产生的两路正弦信号分别为4MHz和5MHz,混频之后产生的信号频率为1MHz和9MHz,首先进行低通滤波设计,我们要把1MHz的信号滤除掉,Filter Solutions软件参数设置如图所示:

参数设定之后生成频响图:

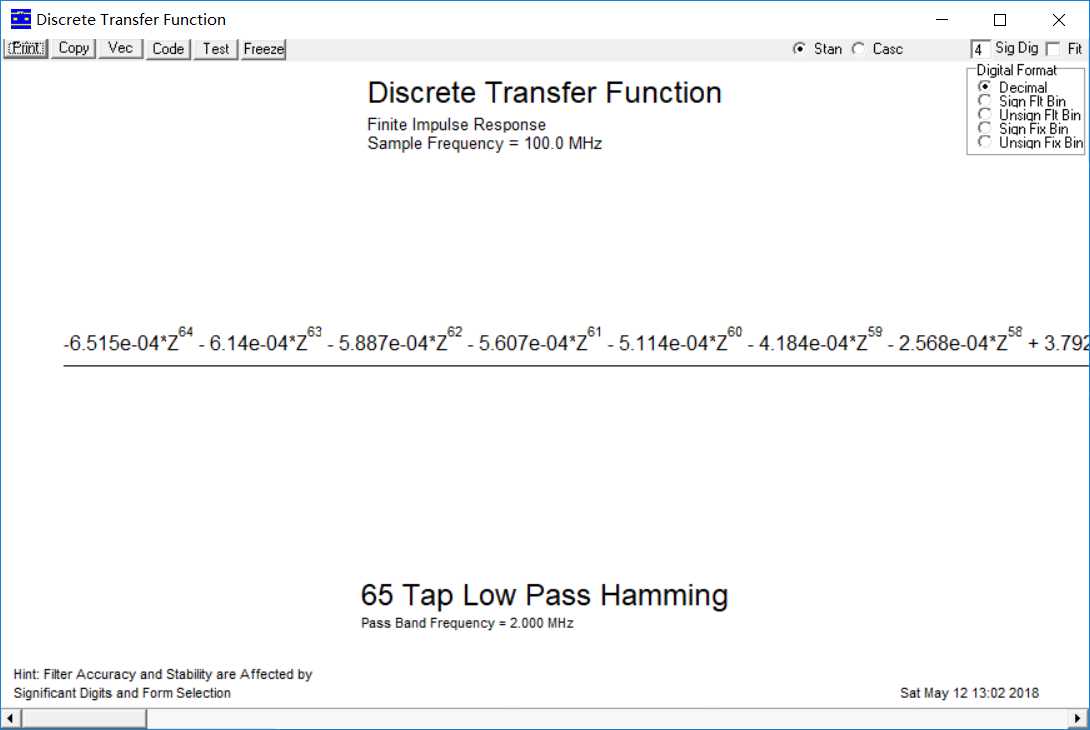

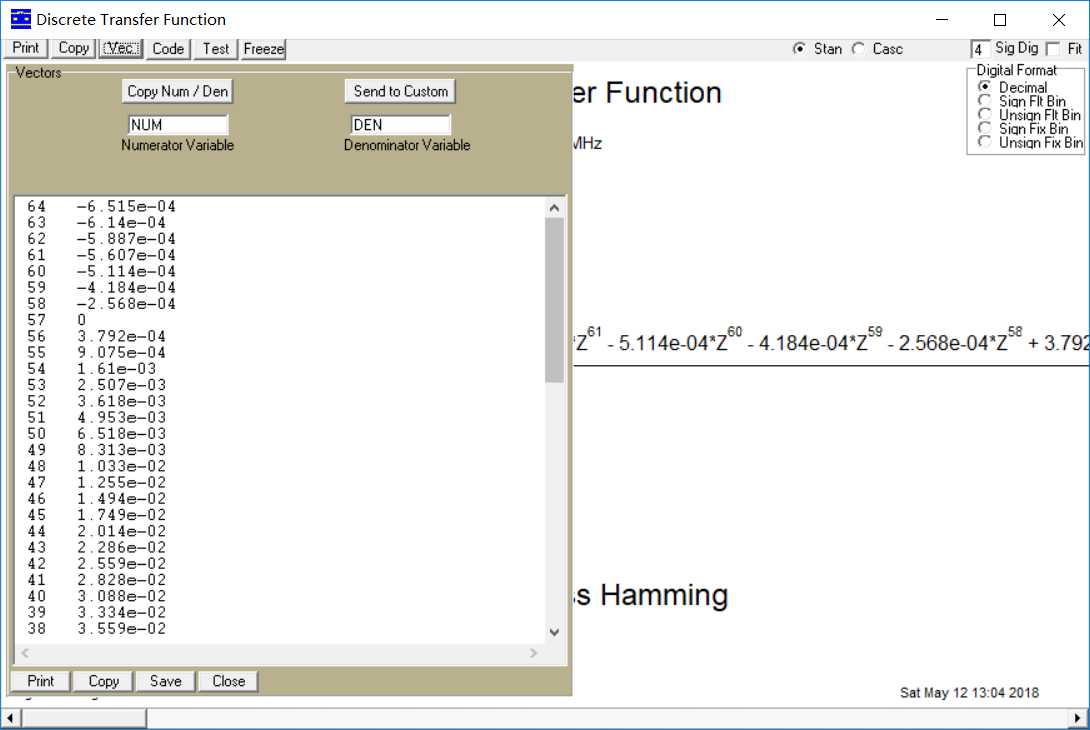

查看相关参数并复制参数:

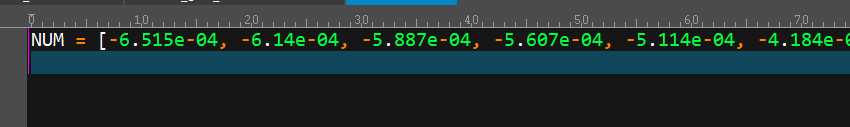

我们把复制的参数粘贴出来可以看到是下面的格式:

[ ]中的数组即为我们需要的参数。

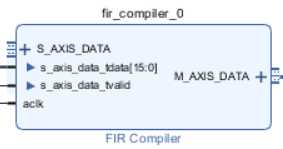

我们在之前的BD程序中,新建一个fir_compiler IP核

双击打开进行相关参数设定:

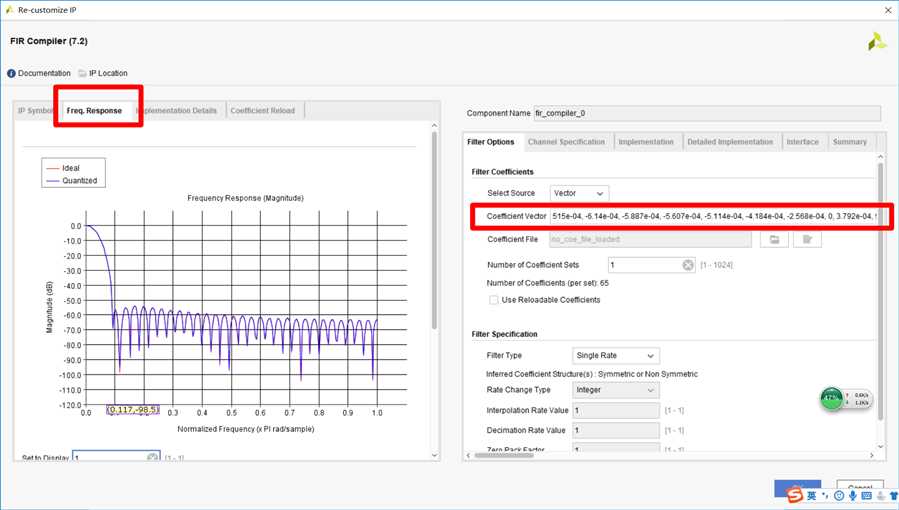

我们把在Filter Solutions软件中得到的参数复制到图中红色框中,在左侧Freq.Response中就可以看到频率响应图

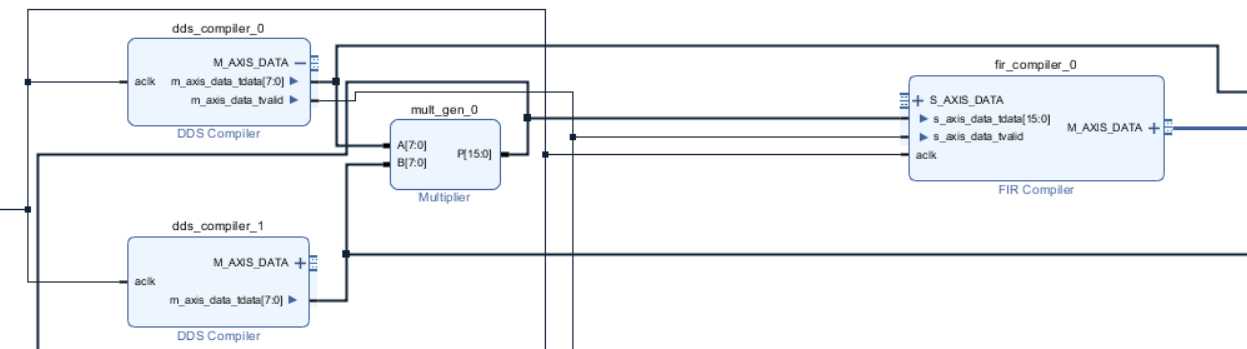

设置好参数之后就可以进行连线操作了,我们将混频之后的信号送给FIR滤波器,连接好时钟和tvalid线

选中FIR的M_AXIS_DATA引脚,右键make external连接管脚,也可以将两路正弦信号连接出来进行观察,连接好之后,valid design没有错误就OK了

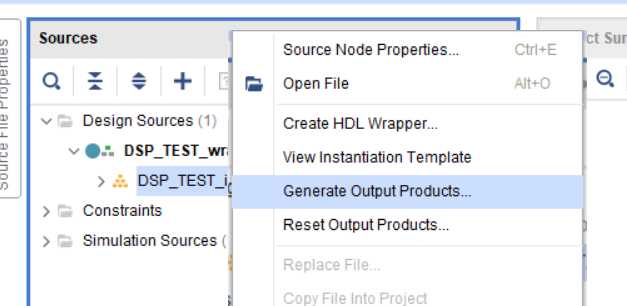

返回到source界面,右键菜单中选中generate output products,更新顶层文件。

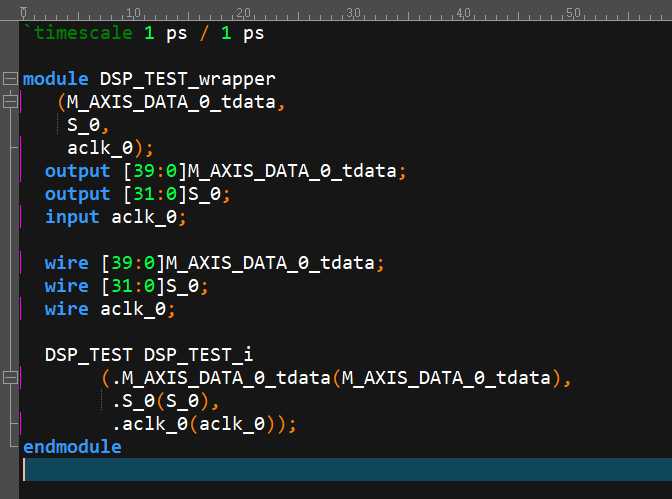

更新之后就可以看到顶层文件中多了一路信号

我们将新增的一路滤波信号添加到仿真文件中即可进行仿真

module tb_top(

);

reg aclk_0 ;

wire [31:0]S_0;

wire[39:0] M_AXIS_DATA_0_tdata;

initial

begin

aclk_0 = 1;

end

always #5 aclk_0 = ~aclk_0 ;

DSP_TEST_wrapper DSP_TEST_wrapper_i

(.M_AXIS_DATA_0_tdata(M_AXIS_DATA_0_tdata),

.aclk_0(aclk_0),

.S_0(S_0));

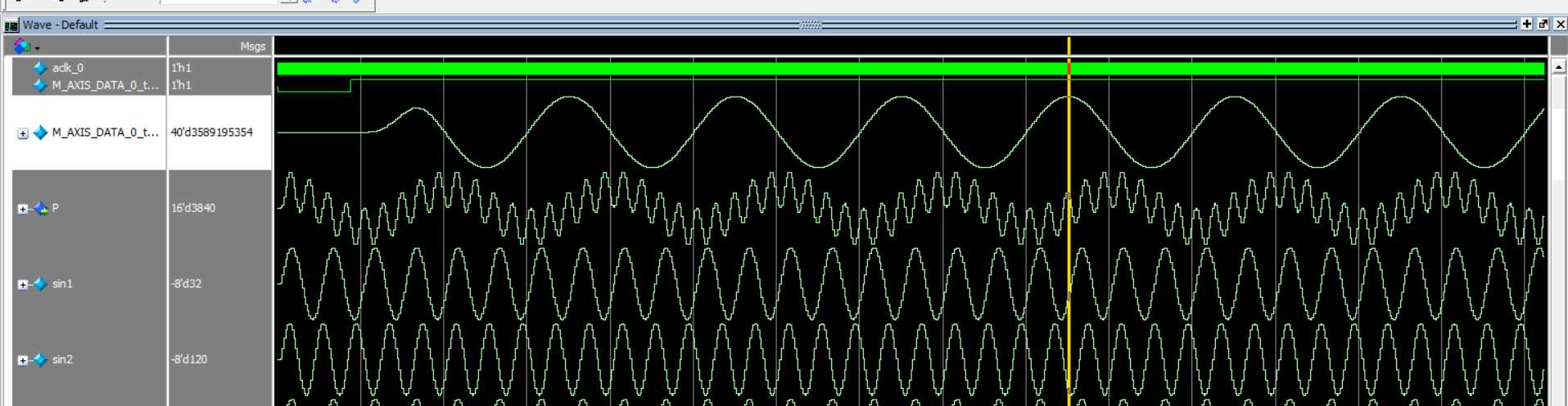

endmodule仿真后添加仿真波形进行查看:

可以看到在仿真结果中,低频信号被滤除了

标签:软件 正弦 class 介绍 make atl inf 文件中 sim

原文地址:https://www.cnblogs.com/chinkwo/p/9028494.html