标签:ble 否则 bubuko 总结 两种 http 原来 技术 height

本篇学习了两种锁存器:SR Latch和D Latch,一种触发器:D flip flop

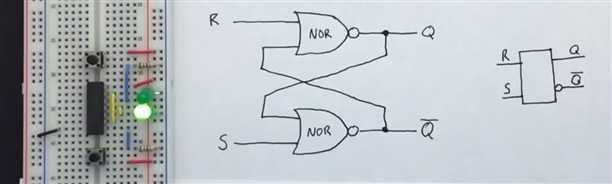

SR Latch:SR—锁存器

初始状态下,S和R都为0,Q和Q‘随机有一个为1另一个 为0(取决于电流速度)。当把S弄成1后,Q为1,此后无论S怎么变化Q都为1。对R也是如此。

一句话总结就是:输出端可以记住S和R最后一次为1的是哪个。这个记住就是存了。

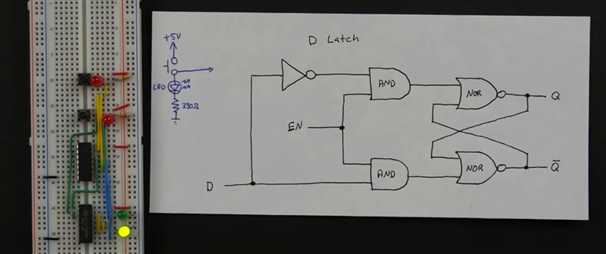

D Latch:D—锁存器

此为对SR锁存器的优化,D相当于原来的S和R,这不但方便操作,还屏蔽了S和R均为1这种不规范操作。

EN是enable的意思,可以控制锁存器是否存D,否则为忽略D数据(不存)

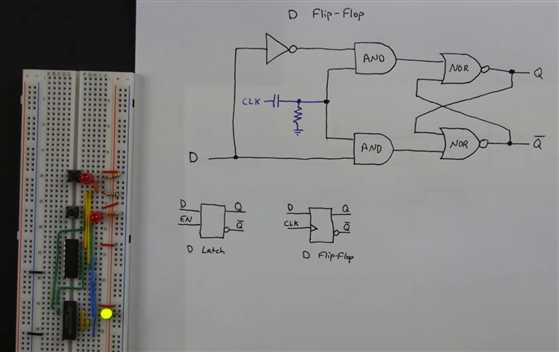

D flip-flop:D—触发器

将D锁存器的EN端改为时钟即为D触发器,功能简单说就是:在时钟上升沿锁存数据

参考视频:eater.net

标签:ble 否则 bubuko 总结 两种 http 原来 技术 height

原文地址:https://www.cnblogs.com/flashsun/p/9532190.html