标签:arm9 传统 cortex-m3 延时 https 接口 执行 追踪 相互

指令和指令系统

指令集架构:

计算机体系结构中与程序设计相关的一部分,包含了一系列的机器指令,基本数据类型,寄存器,寻址模式,存储体系,终端和异常处理等。

是计算机软硬件之间的接口,整个计算机系统建立在指令集架构之上。

每个指令集架构都有各自的开发生态圈(ECO-System),包括芯片设计公司、软件开发环境提供商、嵌入式操作系统提供商、中间件提供商、高校研究人员还有开源社区等

可以分成复杂指令集(CISC)、精简指令集(RISC)、超长指令字指令集(VLIW)等

随着最近几年的发展,CISC和RISC指令集架构也在相互融合

几种常见的指令集架构:

Intel公司推出的Atom系统芯片是面向嵌入式应用市场,是采用x86 IA-32和intel-64可变指令长度的复杂指令集架构的微控制器。

ARMv1架构:诞生于1985年,该版架构只在原型机ARM1出现过,只有26位的寻址空间(64MB),没有用于商业产品。

ARMv2架构:诞生于1986年,首颗量产的ARM处理器ARM2就是基于该架构,包含了对32位乘法指令和协处理器指令的支持,但同样仍为26位寻址空间。其后还出现了变种ARMv2a,ARM3即采用了ARMv2a,是第一片采用片上Cache的ARM处理器。

ARMv3架构:诞生于1990年,第一个采用ARMv3架构的微处理器是ARM6(610)以及ARM7,其具有片上高速缓存、MMU和写缓冲,寻址空间增大到32位(4GB)。

ARMv4架构:诞生于1993年,ARM7(7TDMI)、ARM8、ARM9(9TDMI)和StrongARM采用了该架构。ARM在这个系列中引入了T变种指令集,即处理器可工作在Thumb状态。

Thumb是一种16位的指令集模式。在Thumb模式下,其较短的操作码能提供更好的编码密度,从而能有效地使用有限的存储器带宽。ARM后来的架构都采用了Thumb技术。

从编程的角度看,ARM微处理器的工作状态一般有两种,并可在两种状态之间切换:

ARMv5架构:诞生于1998年,ARM7(EJ)、ARM9(E)、ARM10(E)和Xscale采用了该架构,这版架构改进了ARM/Thumb状态之间的切换效率。此外还引入了DSP指令和支持JAVA。

ARMv6架构:诞生于2001年,ARM11采用的是该架构,这版架构强化了图形处理性能。通过追加有效进行多媒体处理的SIMD将语音及图像的处理功能大大提高。此外ARM在这个系列中引入了混合16位/32位的Thumb-2指令集。

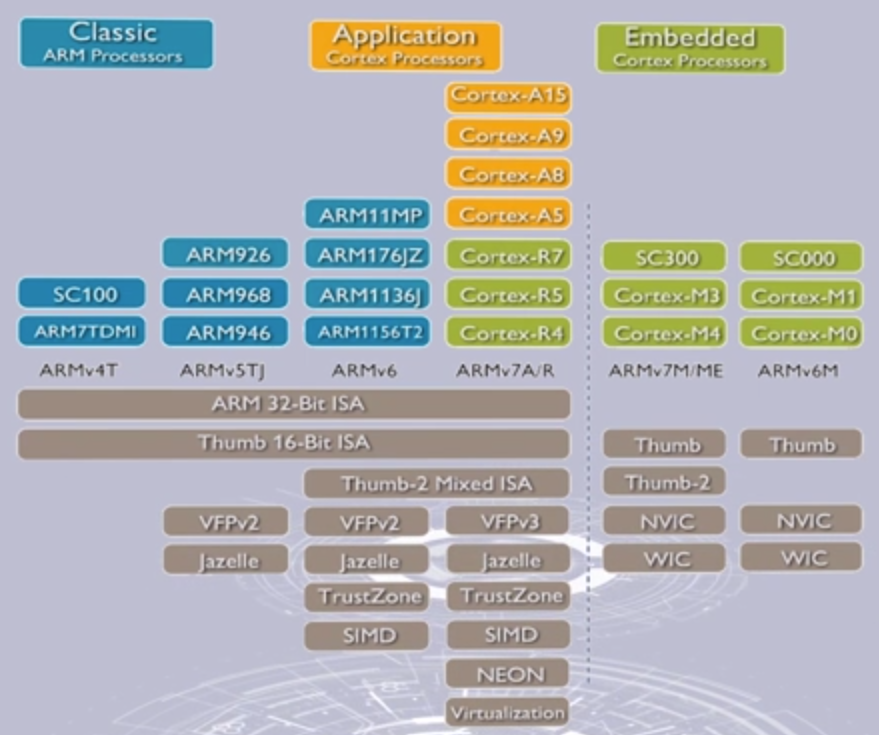

ARMv7架构:诞生于2004年,从这个时候开始ARM以Cortex来重新命名处理器,Cortex-M3/4/7,Cortex-R4/5/6/7,Cortex-A8/9/5/7/15/17都是基于该架构。该架构包括NEON技术扩展,可将DSP和媒体处理吞吐量提升高达400%,并提供改进的浮点支持以满足下一代3D图形和游戏以及传统嵌入式控制应用的需要。

ARMv6-M架构:2007年,为了实现超低功耗的嵌入式处理器,ARM公司基于ARMv6的Thumb指令集和ARMv7-M的异常和调试特性开发出了ARMv6-M架构。Cortex-M0/1/0+采用的该架构。

ARMv8架构:

ARMv8-A 4+64位架构支持引入到ARM指令集架构中,其中包括64位的通用寄存器,堆栈指针寄存器和程序计数器以及64位数据处理和扩展的虚拟寻址,主要有两种执行态,AArch64执行态和AArch32执行态,AArch64针对64位处理技术引入了一个全新的指令集A64,而AArch32执行状态支持现有的ARM指令集,ARMv7全部特性都在ARMv8中得以保留

AArch64 / AArch32支持三个指令集:

Cortex-M处理器采用的是ARMv6-M和ARMv7-M架构,采用较为简单的编程模式,专门为微控制器市场所设置,Cortex-M3/4内核基于ARMv7-M指令集架构。

Cortex-M4可以看作是Cortex-M3的升级版本,两者都是基于32位RISC指令集架构,采用32位寄存器和32位内部数据总线,和其他系列ARM处理器内核不同的是采用的是Thumb-2指令集架构并且不支持传统的ARM指令集。Cortex-M4处理器还支持DSP指令操作和单精度浮点指令,在DSP应用方面具有较高的精度和性能

Cortex-M3/4微处理器内核采用三级流水线设计,分别是指令获取,解码和执行,并且采用哈佛总线架构,即支持指令和数据的同时存取。微处理器采用32位编址,支持4G bit的统一内存地址空间。

微处理器架构:指令集架构(指令集,编程模型和调试方法等)+微架构(设计实现的技术细节包括接口信号,指令执行时序,流水线设计等)

Cortex-M3/4微处理器除了处理器内核之外,还包括嵌套向量中断控制器NVIC

NVIC:寄存器可访问,因此是可编程的。NVIC主要负责异常和中断处理的配置,支持中断优先级和多达240个中断请求源,NVIC依照优先级的顺序处理所有支持的异常和中断,所有的中断和大多数异常可以配置成不同的优先级。当中断发生时,NVIC将比较新中断与当前中断的优先级,如果新中断优先级高,则立即处理新中断,当前正在执行的任务会被暂停,这个过程叫做”抢占“或”中断嵌套“。当异常或中断发生时,Cortex-M处理器会从中断向量表中自动定位异常处理的入口,无需软件进行操作,从而降低从异常发生到处理之间的延时。

基于ARM微处理器的微控制器一般采用AMBA片上总线架构。AMBA高级微控制器总线架构( Advanced Microcontroller Bus Architecture)是用于ARM架构下系统芯片设计中的总线架构。

一个基于AMBA的微控制器内部总线结构包括一个高性能的快速总线AHB或者ASB,为所连接的微处理器、DMA控制器和片上RAM和片外内存之间提供足够的系统带宽,AHB或ASB通过一个总线桥(BRIDGE)和外设总线APB连接,APB总线主要提供外部设备接口电路之间的互联,所提供的系统带宽一般比较低。

微处理器内部还有一个可选的嵌入式跟踪宏单元ETM,ETM宏单元为ARM微处理器提供实时指令跟踪和数据跟踪,跟踪软件工具使用ETM生产的信息可以重现全部或者部分程序执行情况。

ETM:解决系统实时调试问题,程序执行时,ETM通过产生对处理器地址、数据及控制总线活动的追踪来获得处理器的全速操作情况。

标签:arm9 传统 cortex-m3 延时 https 接口 执行 追踪 相互

原文地址:https://www.cnblogs.com/yangyu-IoT/p/12722621.html