标签:系统 parse 技术 状态 不同 pcie ble i2c 使用

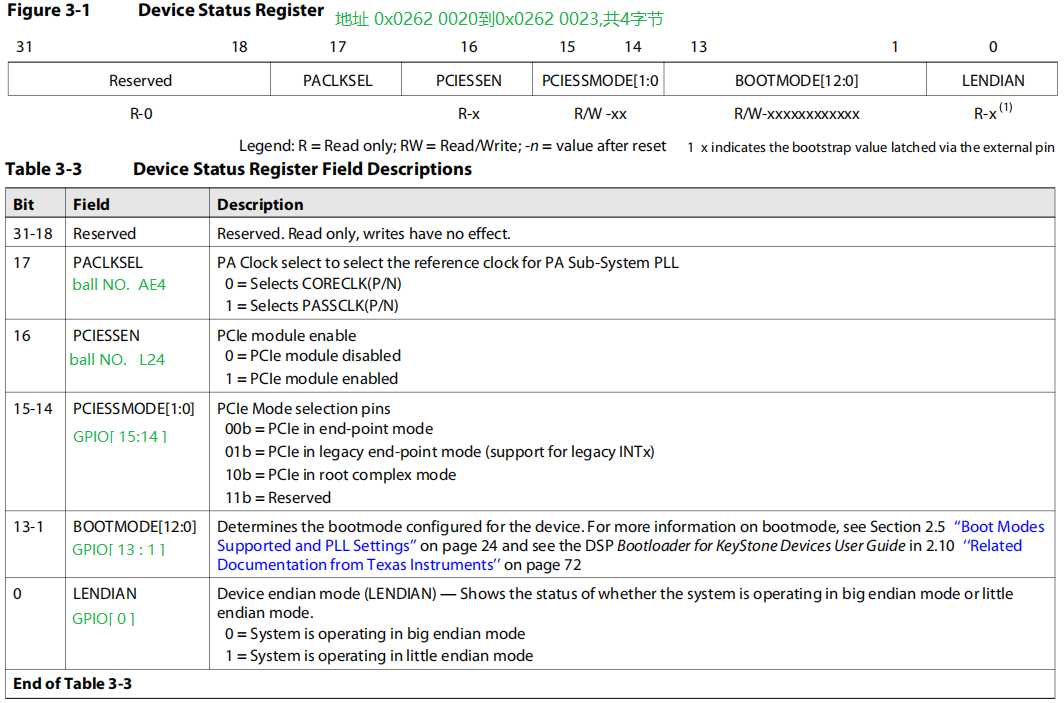

1 DEVSTAT寄存器

1.1 DSP上电复位后,DEVSTAT寄存器自动锁存16个GPIO的值、PACLKSEL引脚值、PCIESSEN引脚值到寄存器内,直到下次上电复位前均保持不变;

DEVSTAT寄存器由硬件设置,辅助Rom Bootloader初始化配置;

1.2 DEVSTAT寄存器逻辑如下:

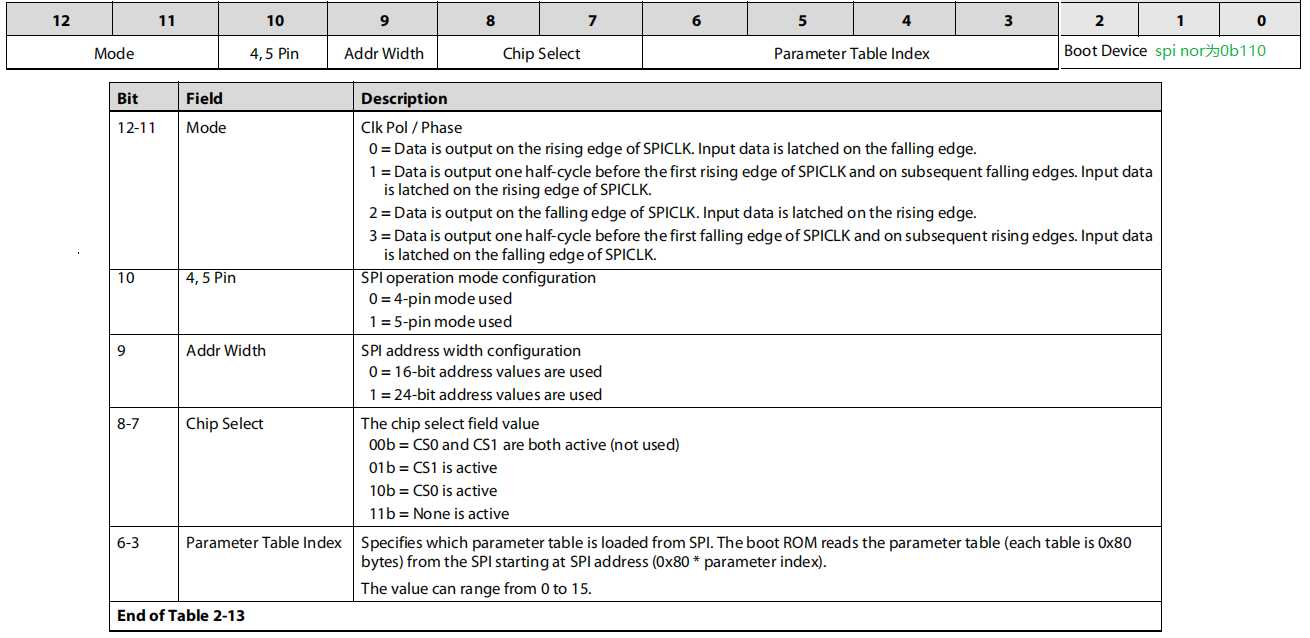

1.3 spi nor的boot模式下,boot mode [ 12:0 ]引脚代表的的逻辑如下表:

1.3.1 无自启动、SPI 启动或者 I2C 方式启动,主 PLL 会被配置为bypass旁路模式;

其他方式启动时,RBL使用bootmode[12:10]去配置主 PLL,(详见数据手册2.5.4 PLL Boot Configuration Settings小节表格);

1.3.2 rom bootloader根据以下参数配置2级bootloader;2级bootloader根据配置,将存储在flash中table格式的程序搬运进共享内存;

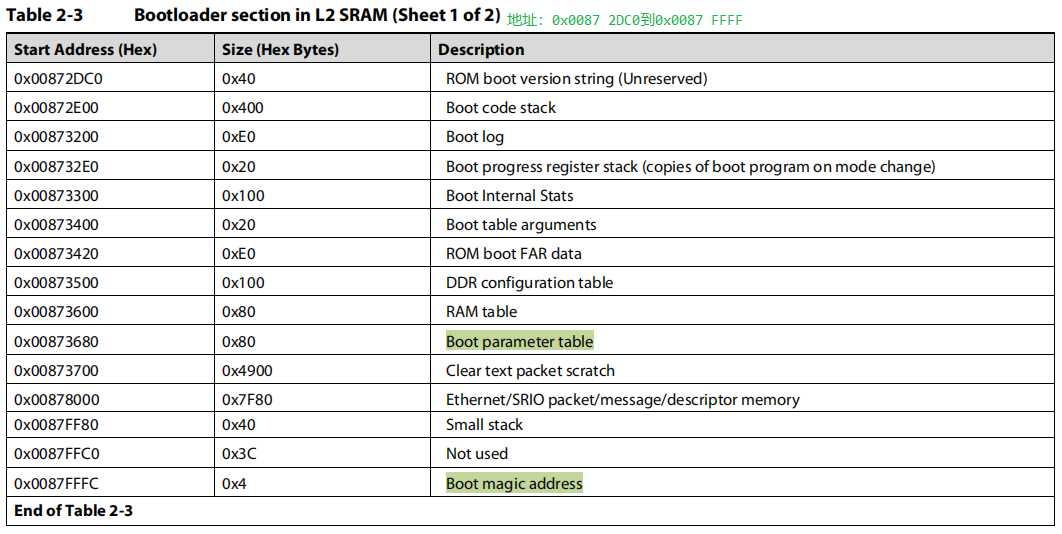

2 boot sequence

2.1 手册说boot sequence是内部存储加载后自动运行的过程;十有八九就是百度上许多论文里说的2级bootloader程序;

boot sequence是RBL向SRAM搬运过程中,在SRAM中用到的一部分地址,用来存储配置以及配置过程中的参数;

Boot magic address就在这里;

3 Rom Bootloader 只读存储器引导加载程序

3.1 Rom Bootloader简称RBL,是通过一系列表格来携带处理信息的程序,程序可以概括为三种表格类型;

3.1.1 可以被RBL处理的三种表格:boot parameter table, boot table, boot configuration table;

存储在外部需要自启动的程序,需要将程序.out文件通过一系列TI提供的转化工具,转化为能被RBL读取.dat或.bin文件;

如何使用工具进行转化的文档:(文档网址,转换工具)

3.1.2 RBL位于L3 ROM内0x20B00000到0x20B1FFFF的地址内,一共128k字节,

DSP上电复位后,首先会进入到ROM中执行bootloader,

然后RBL读取boot parameter table后搬运boot table格式的程序到SRAM中,然后跳转到SRAM中执行程序,

在这个过程中会涉及到配置boot sequence地址中的寄存器;

3.1.3 只有核心0支持RBL的自启动;

其他核心的代码由主内核复制给从内核,然后将从内核的入口地址存入boot_magic_address寄存器,然后向从内核发送一个IPC中断来唤醒从内核;

3.1.3.1 boot loader作用

固化在 ROM 上的代码段会让所有支持重启隔离功能的外设使能重启隔离功能。

固化在 ROM 上的代码段会使能 boot 过程中所有可能需要用到的外设的时钟。

固化在 ROM 上的代码段会利用从 DEVSTAT 寄存器三个 PLL 比特中读取的信息配置系统 PLL。

RBL会在L2缓存中为每个核心预留出程序代码的存储空间,EMIF16模式则不会预留;

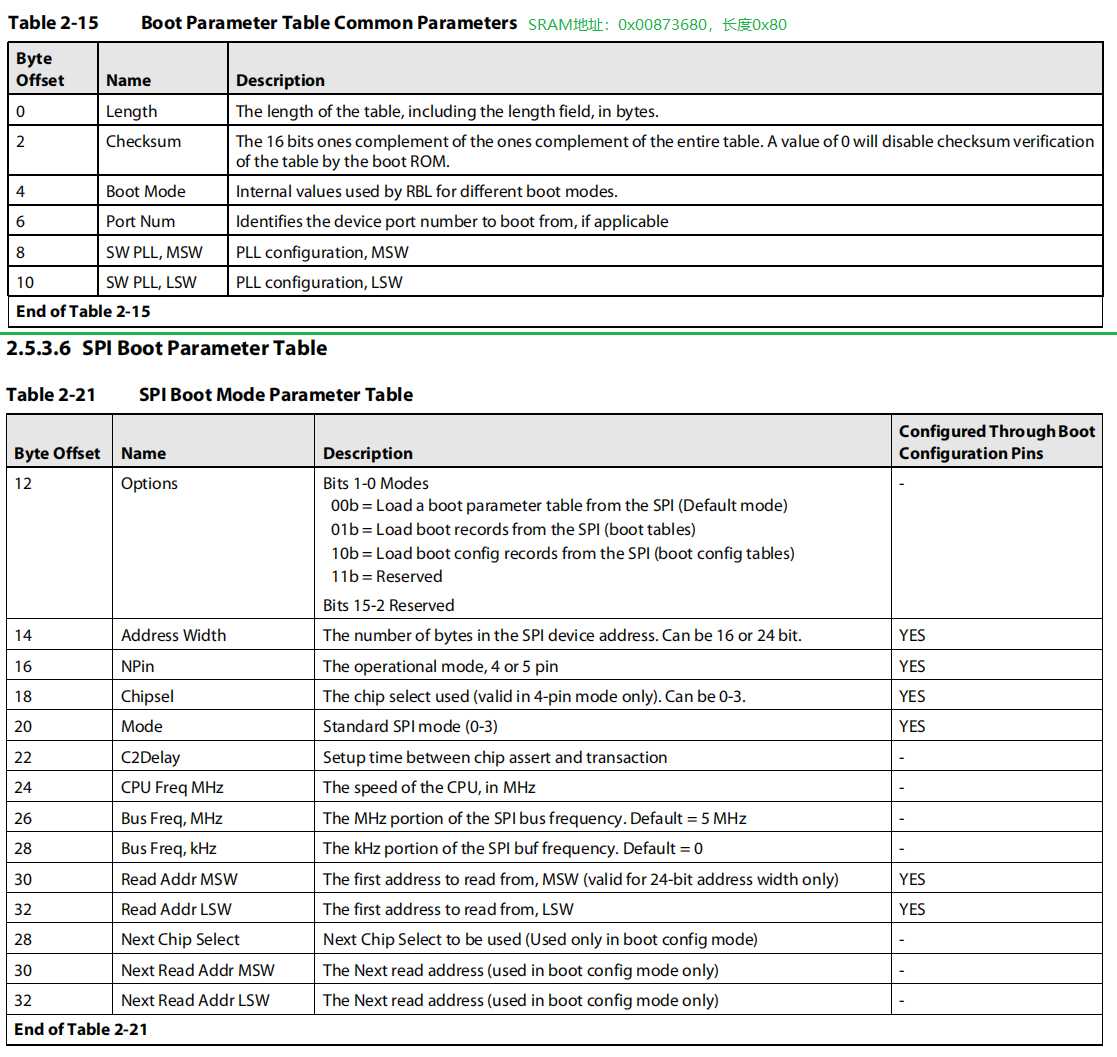

3.2 boot parameter table

3.2.1 作用:上电复位的时候初始化PLL配置或者选择bypass模式;配置RBL的不同模式下的工作参数;

3.2.2 对于spi nor的boot模式而言,剩下的参数是在转化.out文件的时候由romparse.exe的辅助文件nysh.spi.map补充的;

3.3 boot table

3.3.1 作用:将程序拆分成可以被RBL识别的程序段,

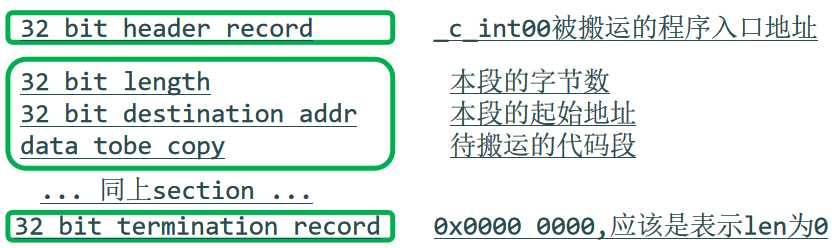

3.3.2 格式:如下所示为boot table的格式

第一个header里存储了程序搬运到SRAM后的入口地址;当RBL搬运到段的length为0字节时,完成搬运,跳转到_c_int00地址执行程序代码;

3.4 boot configuration table

3.4.1 作用:当需要外设的配置与复位状态不同时,可以通过boot configration table来配置;

比如可以用boot configration table来初始化配置DDR,然后就可以将程序加载进DDR中了;

(我们的程序是搬运到4M共享内存中的,不是DDR3中的,所以没有用到boot configuration table)

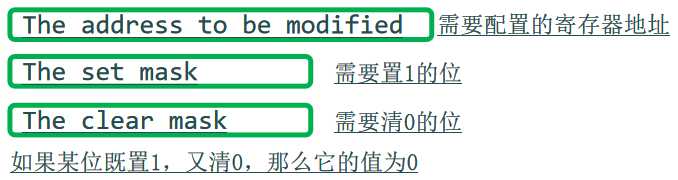

3.4.2 格式:boot configuration table可以有许多项(entry),每个项有3个元素如下所示,当项的三个元素都为0的时候,表示结束;

标签:系统 parse 技术 状态 不同 pcie ble i2c 使用

原文地址:https://www.cnblogs.com/caesura-k/p/12804842.html