标签:分析工具 quartus info lock com 高级 lan 时间 最小化

派生时钟就是和独立时钟存在频率或者相位关系的时钟,异步存储器就是具有存储读写异步功能的存储器。在时序分析中,这两个部分的静态时序分析是需要设置个别约束的。派生时钟会产生时钟偏斜或者不同频率时序问题,异步存储器则类似latch,存在建立时间和保持时间的要求。

分别对独立时钟和衍生时钟做时序约束,保证其能够进行STA分析

(1)多周期约束定义

一般的时钟约束都是基于一个时钟周期的,以一个周期的边沿为数据变化条件。对于某些特殊的路径,可以以多个周期为触发条件,以便达到提高建立时间和调节保持时间的目的。具体到RTL层次上就是用一个技术信号控制时钟边沿是否读取数据。

(2)多周期约束方法

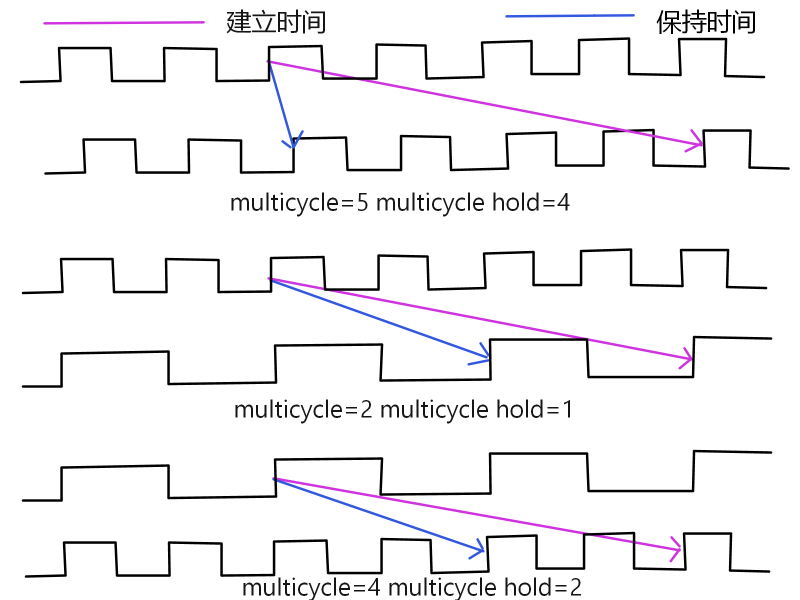

多周期约束需要设置的参数有两个:multicycle和multicycle hold;第一个是多少个时钟周期触发一次,直接对应建立时间,第二个是多少个周期保持不变。具体的方法还是在实际设计中操作。

(3)时钟使能

对于时钟使能信号,可以通过多周期约束模拟信号的触发间隔,可以提高静态时序的精确性。

(4)多周期约束的条件

多周期约束应当保证数据延时在保持时间和建立时间之间,这样才能满足时序约束。

(5)具体问题处理

1??同频偏置信号

2??高频信号到低频信号(存在倍频关系)

3??低频信号到高频信号(存在倍频关系)

1??cut off foodback from I/O pins

去除双向IO的伪路径(从输入寄存器到输出寄存器)

2??cut clear and preset paths

切除异步复位和置位端路径

3??cut off read during write signals paths

不分析ESB(嵌入式系统块)路径

4??cut paths between unrelated clocks

非相关时钟会被减除,需要和系统时钟建立关系约束

5??cut timing path

手动去除路径分析

(1)使用多周期约束(2)减小偏斜skew(3)增加数据延时

时序约束的目标就是在预设时钟周期下,完成所有路径的建立时间和保持时间的成立等式。

在静态时序分析时需要减除异步时钟域,使用伪路径实现两个时钟域的各自静态时序分析。一般的跨时钟域的通行采用握手信号的形式,具体的内容可以参考另外一篇笔记FPGA中的时钟域问题。

quartsu中的时序分析报告默认在最差的情况下的时序分析,高温、低工艺、低压的状态下。也可以通过设置完成最小化时序分析(也就是最佳状况下的分析),注意会刷新原来的一般时序报告。约束方法就是在timing setting中设置好最小化的tsu、th和tpd,然后在tcl中输入 quartus_tan --min <project name>就可以实现最小化时序分析。

quartus中支持TCL脚本语言,可以实现所有时序约束的操作。

TimeQuest是quartus中的时序分析工具,能够分析不断发展的器件,相较于原先的tan,可以更好地完成静态时序分析。

标签:分析工具 quartus info lock com 高级 lan 时间 最小化

原文地址:https://www.cnblogs.com/electricdream/p/13637440.html